# ANSI EIA/TIA-530-A

### In this report:

Electrical Characteristics ..... 7

*Note:* The content of this report has been reviewed and revalidated. It is being published with a new date to indicate that the information is current.

### **Datapro Summary**

ANSI EIA/TIA-530-A (hereafter EIA-530-A) defines the mechanical interface characteristics between Data Termination Equipment (DTE) and Data Circuit-Terminating Equipment (DCE). It operates in conjunction with RS-422-A and RS-423-A, which define the electrical operation of the individual interchange circuits for balanced and unbalanced operation, respectively. EIA-530-A complements RS-232-D for data rates above 20K bps and replaces RS-449 for data rates above 20K bps.

A revision of EIA-530, EIA-530-A was approved in May 1992 and includes several relatively minor modifications to the previous standard. The most significant change accounts for the alternative 26-position interface connector (Alt A). Other revisions comprise the following:

- Addition of Circuits CJ (Ready for Receiving), CE (Ring Indicator), and AC (Signal Common).

- Use of Circuit CB (Clear to Send) for hardware flow control.

- Use of Local Loopback for "Busy Out."

- Change of Circuits CC (DCE Ready) and CD (DTE Ready) to Category II Circuits.

The new standard is compatible with EIA-530, but applications connecting versions of RS-449 or EIA-530 (with Category I Circuits CC and CD) with EIA-530-A (with Category II Circuits CC and CD) require an unbalanced/balanced converter between the interfaces (see Table "Interconnecting EIA RS-530-A With EIA RS-449" for circuitry connections).

In 1977 the Electronic Industries Assn. (EIA) developed the RS-449, RS-422, and RS-423 standards to eventually replace RS-232-C. RS-449, however, never really caught on and, in March 1987, EIA-530 was introduced as its intended replacement. RS-422 and RS-423 remain in the revised forms of RS-422-A and RS-423-A. RS-232-C also outlasted RS-449 and, in January 1987, the EIA issued RS-232-D, a revision for RS-232-C.

EIA-530-A governs the mechanical and electrical characteristics of the interface between Data Terminal Equipment (DTE) and Data Circuit-Terminating Equipment (DCE). The standard defines DTE as the hardware on the business machine side of the interface (teleprinters, display terminals, front-end processors, central processing units, etc.), and DCE as the modem, signal converter, or other device between the DTE and the communications line.

This report compares EIA-530-A with RS-232-D, RS-449, and CCITT V.35. It also discusses the mechanical and electrical characteristics and looks at the general classification of interchange circuits and outlines interchange circuit details.

Copies of EIA-530-A, RS-422-A, and RS-423-A can be obtained from the Electronic Industries Assn., 2001 I Street NW, Washington, DC 20006.

## Analysis

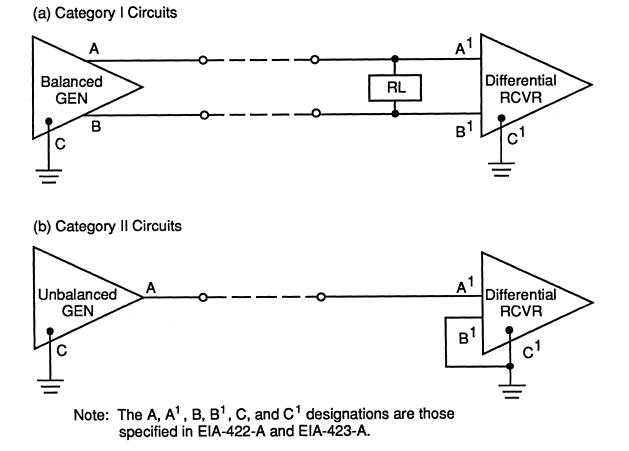

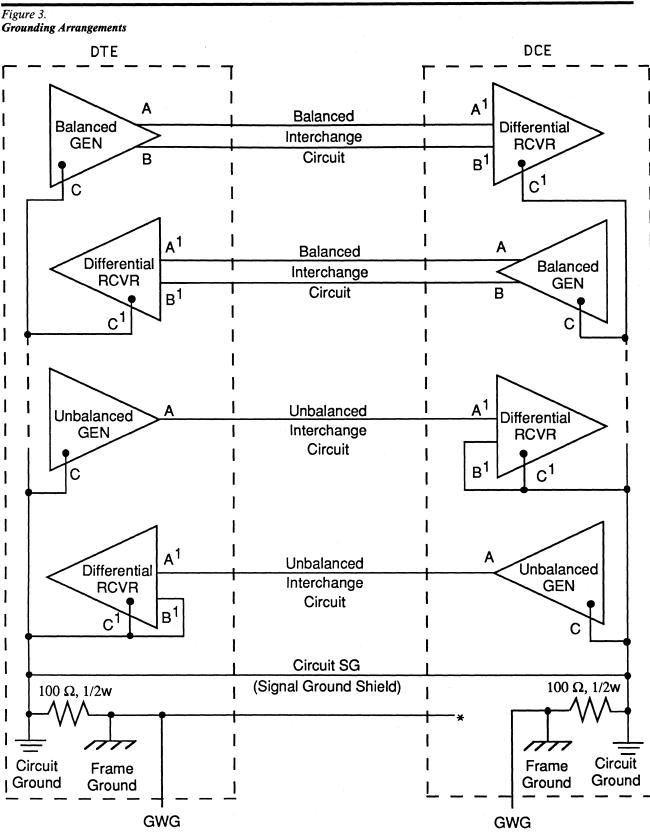

EIA-530-A operates in conjunction with either of two standards specifying electrical characteristics: RS-422-A, for balanced circuits; and RS-423-A, for unbalanced circuits. When each interface circuit has its own ground lead, the circuit is balanced. When an interface uses a common or shared grounding technique, it is unbalanced.

EIA-530-A is used for data communications systems with the following characteristics:

- 2747 Standards

- DTE serializes data bits, and the DCE puts no restrictions on the DTE's bit sequence arrangements.

- Communication is binary, serial, synchronous, or asynchronous, and control information is exchanged on separate circuits.

- Equipment on one side of the DTE/DCE interface connects directly to equipment on the other side without additional technical considerations.

- Communication is in half- and/or full-duplex modes in pointto-point or multipoint configurations over two- or four-wire facilities with data rates ranging from 20K bps to a nominal upper limit of 2.1M bps. Point-to-point arrangements may operate on either switched or dedicated facilities. Dedicated lines connect multipoint arrangements.

Applications in which cable termination, signal wave shaping, interconnection cable distance, and the interface's mechanical configurations must be tailored to meet specific user needs are not precluded, but are generally not within the standard's scope. The EIA-530-A connector, also used for RS-232-D, uses electrical characteristics that, if improperly connected to some silicon devices designed to meet the RS-422-A and RS-423-A electrical characteristics specified in this recommendation, could damage those devices.

### EIA-530-A/RS-232-D

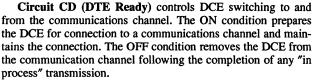

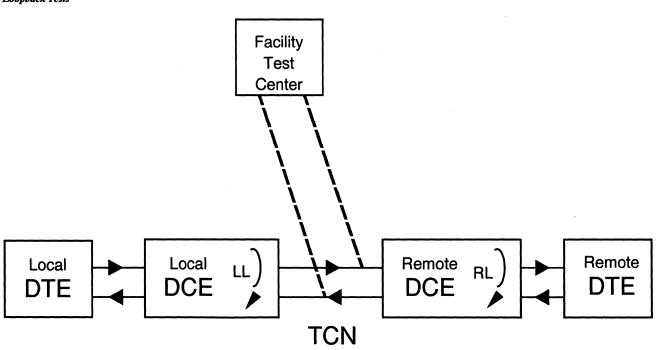

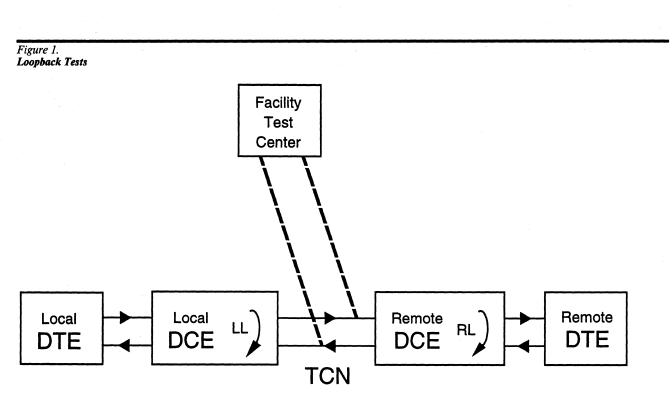

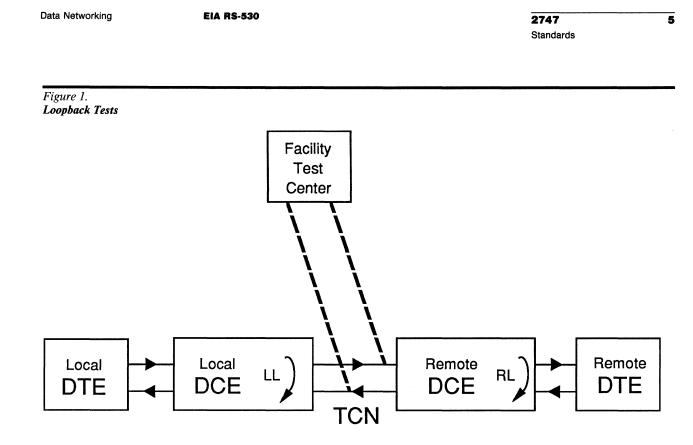

These standards include a specification of the D-shaped 25-pin interface connector, which RS-232-C had only referenced in an appendix and never included as part of the standard. Both standards support testing of both local and remote DCEs through the Local Loopback, Remote Loopback, and Test Mode circuits. Circuit names for the first 8 pins in both standards are the same, but differ on pins 9, 10, and 11, which are not used in RS-232-D.

RS-530-A achieves higher data rates than RS-232-D (greater than 20K bps) by specifying the use of balanced signals, while sacrificing some secondary signals and the Ring Indicator. The Ring Indicator's elimination indicates that EIA-530-A is not for use in dial-up applications.

### EIA-530-A/RS-449

The EIA-530-A standard has officially replaced RS-449 but, while both standards are in use, EIA-530-A can be interconnected with RS-449 devices through a connecting cable or adapter. Table *"Interconnecting EIA RS-530-A With EIA RS-449"* lists the circuit name and mnemonic, and connector contact pin for each interface.

### EIA-530-A/CCITT V.35

EIA-530-A provides balanced (EIA-422-A) generators and receivers on interchange Circuits CA (Request to Send), CB (Clear to Send), and CF (Receive Line Signal Detector). The corresponding interchange circuits in a V.35 interface utilize CCITT V.28 (EIA-232-E) electrical characteristics. In applications connecting an EIA-422-A balanced generator with an EIA-232-E unbalanced receiver, a special balanced/unbalanced converter must be employed between the interfaces. Otherwise, EIA-530-A and CCITT V.35 are fully compatible.

### **Mechanical Characteristics**

The point of demarcation between the DTE and the DCE is at connector plugs on the DCE or at an interface point no further than ten feet (three meters) from the DCE. A 25-position connector was specified for all interchange circuits in EIA-530. EIA-530-A's alternative 26-position "Alt A" connector is specified for

use when a smaller physical connector is required (it is approximately  $\frac{3}{4''} \times \frac{1}{4''}$ ). In all cases, the DTE provides the cable (up to 200 feet), which has male (pin) contacts and a female shell (plug connector); the DCE has a female connector. The connectors are equipped with a block that permits latching and unlatching without a tool. The latching block also permits the use of screws to fasten the connectors together. The mechanical configuration for connections of the interface cable at points other than the demarcation point is not specified.

When additional functions are offered in a separate unit that is inserted between the DTE and DCE, the female connector is associated with the DTE interface, while the male connector is a DCE interface.

### Functional Description of Interchange Circuits

Interchange circuits fall into four general classifications: ground (or common return), data circuits, control circuits, and timing circuits. Table "EIA RS-530-A Interchange Circuits" outlines a list of EIA-530-A interchange circuit showing circuit mnemonic, circuit name, circuit direction, and circuit type. Table "RS-530 and Nearest Equivalent CCITT V.35" compares the connector pin assignments and the functional interchange circuits along with an equivalency table showing the nearest equivalent CCITT V.35 functions in relation to each EIA-530-A function. A functional description of each of the EIA-530-A interchange circuits follows.

### **Ground or Common Return Circuits**

Circuit AB and AC (Signal Commons) connects the DTE circuit ground (signal common) to the DCE circuit ground (signal common) to provide a conductive route between the DTE and DCE signal commons.

### **Data Circuits**

**Circuit BA (Transmitted Data)** transfers the data signals originated by the DTE to the DCE. The DTE holds Circuit BA in the binary ONE (marking) condition unless an ON condition is present on all of the following circuits: CA (Request to Send), CB (Clear to Send), CC (DCE Ready), and CD (DTE Ready). The DCE disregards any signal appearing on Circuit BA when an OFF condition exists on one or more of these circuits. While an ON condition is maintained on each of the circuits, the DCE sends all data signals transmitted across the interface on Circuit BA to the communications channel. The term "data signals" includes the binary ONE (marking) condition, reversals, and other sequences, such as SYN coded characters that maintain timing synchronization.

**Circuit BB (Received Data)** transfers DCE-generated data signals to the DTE in response to line signals from a remote station. Circuit BB is held in the binary ONE (marking) condition while Circuit CF (Receive Line Signal Detector) is in the OFF condition. On half-duplex channels, Circuit BB is held in the marking condition when Circuit CA is ON and for a brief interval when Circuit CA makes the transition from ON to OFF. This allows for the completion of the transmission and for the decay of channel reflections.

### Timing Circuits

**Circuit DA (Transmit Signal Element Timing—DTE Source)** provides the DCE with transmit signal element timing data. The ON to OFF transition nominally indicates the center of each signal element on Circuit BA. When Circuit DA is implemented in the DTE, the DTE provides timing data on it whenever the DTE is

ALC: NOW

Contraction of the local division of the loc

## Interconnecting EIA RS-530-A With EIA RS-449

| Mnemonic |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EIA-RS-449                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | Contact                                                                                                                                                                                                                    | Contact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Circuit Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| None     | 1                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Shield                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| BA (A)   | 2                                                                                                                                                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SD (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Send Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| BA (B)   | 14                                                                                                                                                                                                                         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SD (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| BB (A)   | 3                                                                                                                                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RD (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Receive Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| BB (B)   | 16                                                                                                                                                                                                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RD (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CA (A)   | 4                                                                                                                                                                                                                          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RS (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Request to Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CA (B)   | 19                                                                                                                                                                                                                         | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RS (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CB (A)   | 5                                                                                                                                                                                                                          | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CS (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Clear to Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| CB (B)   | 13                                                                                                                                                                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CS (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| сс       | 6                                                                                                                                                                                                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DM (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data Mode (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|          |                                                                                                                                                                                                                            | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DM (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CD       | 20                                                                                                                                                                                                                         | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TR (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Terminal Ready (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|          |                                                                                                                                                                                                                            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TR (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| AB       | 7                                                                                                                                                                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Signal Ground (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| CF (A)   | 8                                                                                                                                                                                                                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RR (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Receiver Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| CF (B)   | 10                                                                                                                                                                                                                         | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RR (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| DB (A)   | 15                                                                                                                                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ST (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Send Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| DB (B)   | 12                                                                                                                                                                                                                         | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| DD (A)   | 17                                                                                                                                                                                                                         | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RT (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Receive Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| DD (B)   | 9                                                                                                                                                                                                                          | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RT (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| LL       | 18                                                                                                                                                                                                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Local Loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| RL       | 21                                                                                                                                                                                                                         | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Remote Loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| DA (A)   | 24                                                                                                                                                                                                                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TT (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Terminal Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| DA (B)   | 11                                                                                                                                                                                                                         | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TT (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| ТМ       | 25                                                                                                                                                                                                                         | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ТМ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |