THE AES - 80 MICROPROCESSOR

## REFERENCE MANUAL

AUTOMATIC ELECTRONIC SYSTEMS INC., 5455 PARE ST., MONTREAL 309 CANADA, TEL. (514) 735-6581 AES DATA INC., P.O. BOX 143 ST ALBANS, VERMONT 05478, TEL. (802) 524-3660

# 8 Ø

# MICROPROCESSOR REFERENCE MANUAL

PROPRIETARY NOTICE: This publication contains proprietary information of Automatic Electronic Systems Inc. and shall not be reproduced, copied, or used for any purpose other than the consideration of technical content without the express written permission of a duly authorized representative of Automatic Electronic Systems Inc.

AUTOMATIC ELECTRONIC SYSTEMS INC., 5455 Pare Street Montreal 309

TEL.: (514) 735-6581

#### AES MICROPROCESSOR

#### TABLE OF CONTENTS

|             |                   |                                         | Page                              |

|-------------|-------------------|-----------------------------------------|-----------------------------------|

| I.          | System            | Design Featu <b>res</b>                 | 1                                 |

|             |                   |                                         |                                   |

|             | l.Ø               | General Characteristics                 | 1                                 |

|             | 1.1               | Physical Configuration                  | 1                                 |

|             | 1.2               | System Organization                     | 2                                 |

|             | 1.3               | Instruction Memory                      | 1<br>2<br>2<br>3<br>4<br>4        |

|             | 1.4               | Data Memory                             | 3                                 |

|             | 1.5               | Arithmetic Logic Unit                   | 4                                 |

|             | 1.6               | Registers                               |                                   |

|             |                   | 1.6.Ø P-Register                        | 4<br>4                            |

|             |                   | 1.6.1 A-Register                        | 4                                 |

|             |                   | 1.6.2 L-Register                        | 4                                 |

|             |                   | 1.6.3 LA-Register                       | - 5                               |

|             |                   | 1.6.4 B-Register                        | 5                                 |

|             | *                 | 1.6.5 U-Register                        | 5                                 |

|             | 1.7               | Decision Flags                          | <b>4</b><br>5<br>5<br>5<br>5<br>6 |

|             | 1.8               | Push Down Stack                         | 6                                 |

|             | 1.9               | Instruction Timing                      | 6                                 |

|             | 1.1ø              | Input/Output Interface                  | 6                                 |

| II.         | Microin           | nstruction Repertoire                   | lØ                                |

|             | <b>2</b> <i>d</i> | Turkungting Normala                     | 1 01                              |

|             | 2 <b>.</b> Ø      | Instruction Formats                     | 1Ø                                |

|             |                   | 2.Ø.Ø Function<br>2.Ø.1 Decision        | 1Ø                                |

|             |                   | 2.0.1 Decision                          | 1Ø                                |

|             |                   | 2.Ø.2 ROM Address<br>2.Ø.3 RAM Address  | 11<br>11 '                        |

| · · ·       |                   | 2.Ø.4 Data Literal                      | 11                                |

| · · · · · · |                   | 2.Ø.5 ALU Literal                       | 12                                |

|             | 2.1               | Terms, Mnemonics and Symbols            | 12                                |

|             | 2.2               | Load Data Bus Instructions              | 13                                |

|             | 2.3               | Load Literal Buffer Instruction         | 14                                |

|             | 2.4               | ALU Mode Instruction                    | 14                                |

|             | 2.5               | Load Accumulator Instructions           | 17                                |

|             | 2.6               | RAM Address Instructions                | 17                                |

|             | 2.7               | Store Into RAM Instruction              | 18                                |

|             | 2.8               | Conditional Branch Instructions         | 18                                |

|             | 2.9               | Set Page Instruction                    | 19                                |

|             | 2.1Ø              | Unconditional Jump Instruction          | 19                                |

|             | 2.11              | Jump to Subroutine Instruction          | 2ø                                |

|             | 2.12              | Return from Subroutine Instruction      | 2ø                                |

|             | 2.13              | NOP and HALT Instructions               | 2ø                                |

|             | 2.14              | PORC and the RST Instruction            | 21                                |

|             | 2 15              | Real TIME CLOCK and the BTC Instruction |                                   |

| III. | Input                                           | c/Output                                                                                                                                                                                                                                                                                                                                                                    | Page<br>23                                                              |

|------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|      | 3.ø<br>3.1<br>3.2<br>3.3<br>3.4                 | Parallel I/O<br>Multiprocessor Configuration<br>I/O Instructions<br>3.4.1 U-Register Instructions<br>3.4.2 I/O Register Select Instructions<br>3.4.3 I/O Channel Select Instruction<br>3.4.4 Serial I/O Clock, Load and R/W<br>Instructions<br>3.4.5 Relinquish Bus Control Instructions<br>3.4.6 Serial I/O Timing Instructions<br>3.4.7 Interrupt Instructions            | 29<br>3Ø                                                                |

| IV.  | Timir                                           | 3.4.8 Other I/O Instructions                                                                                                                                                                                                                                                                                                                                                | 31                                                                      |

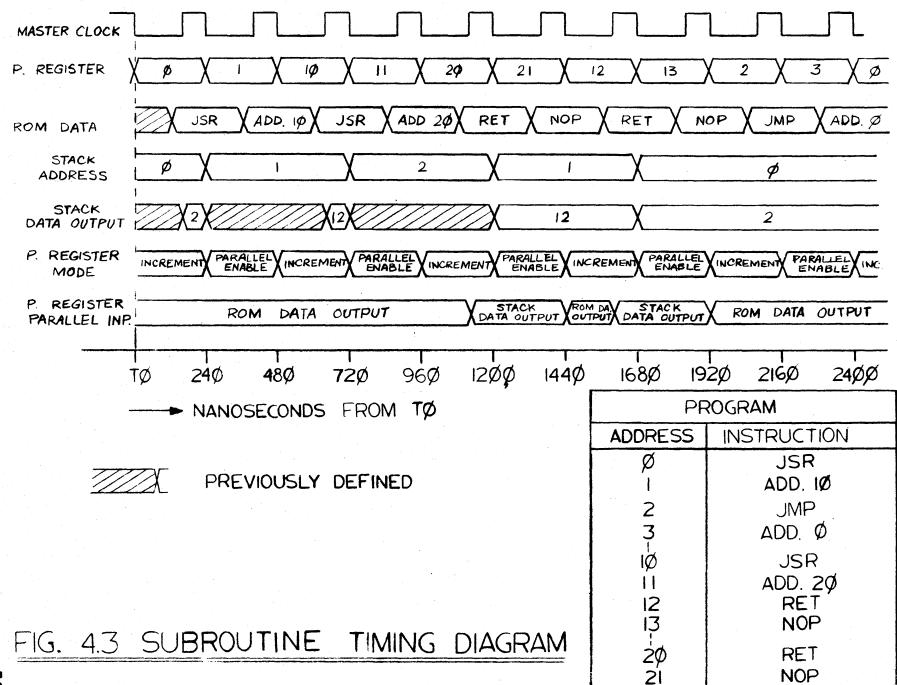

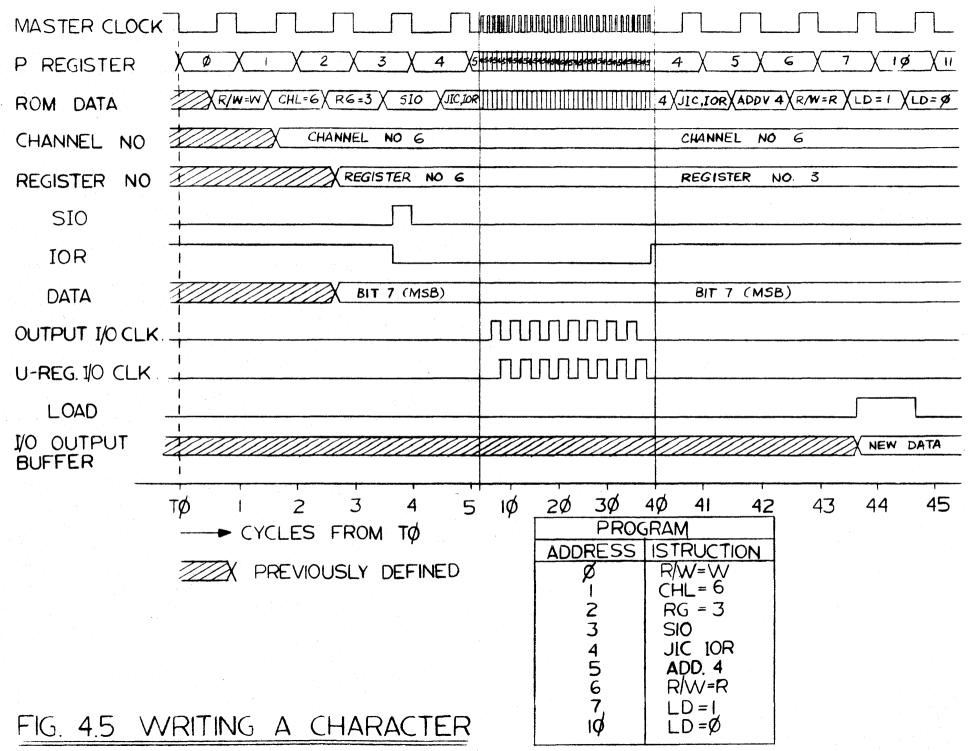

|      | 4.Ø<br>4.1<br>4.2<br>4.3                        | Function and Literal Timing<br>Branch Instruction Timing<br>Subroutine Timing<br>I/O Timing                                                                                                                                                                                                                                                                                 | 35<br>35<br>35<br>35                                                    |

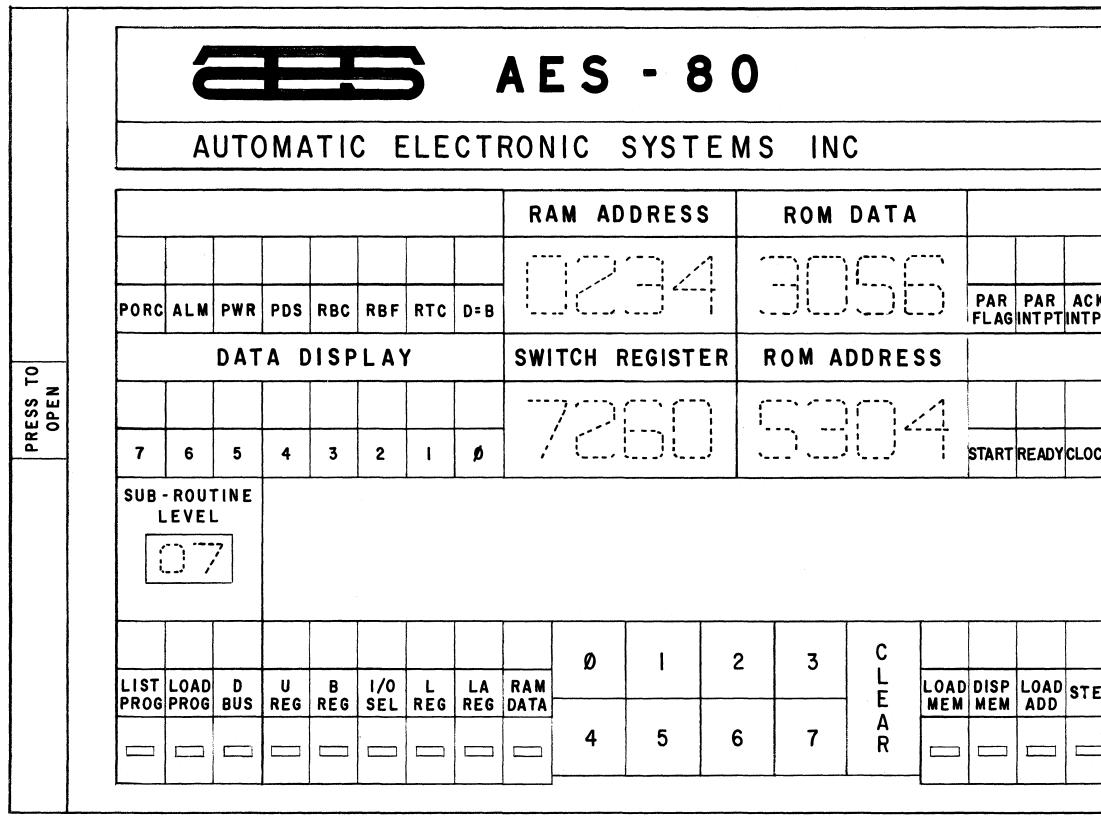

| v.   | Progr                                           | cam Development and Control Console                                                                                                                                                                                                                                                                                                                                         | 41                                                                      |

| VI.  | Softw                                           | vare Development                                                                                                                                                                                                                                                                                                                                                            | 45                                                                      |

| VII. | Apper                                           | ndices                                                                                                                                                                                                                                                                                                                                                                      |                                                                         |

|      | A.1<br>A.2                                      | Table of Binary to Octal to ASCII Convers:<br>Operation Code List                                                                                                                                                                                                                                                                                                           | ion A.1<br>B.1                                                          |

|      | Illus                                           | strations                                                                                                                                                                                                                                                                                                                                                                   |                                                                         |

|      | 1.1 1.2 2.1 3.1 3.2 3.3 4.1 4.2 4.3 4.4 4.5 5.1 | Microprocessor Block Diagram<br>Master Clock Timing<br>Functional Programming Block Diagram<br>Typical I/O System Configuration<br>MSU Bus Interface<br>Typical I/O Interface Card<br>Function Timing Diagram<br>Branch Instruction Timing Diagram<br>Subroutine Timing Diagram<br>Reading a Character<br>Writing a Character<br>Program Development and Control Console Pa | 8<br>9<br>22<br>32<br>33<br>34<br>36<br>37<br>38<br>39<br>4Ø<br>anel 44 |

|      |                                                 |                                                                                                                                                                                                                                                                                                                                                                             |                                                                         |

#### SYSTEM DESIGN FEATURES

#### 1.Ø. General Characteristics

1.

1.

The AES microprocessor is a byte oriented general purpose computer designed primarily for OEM use in dedicated applications. The main features and characteristics which describe its operation can be summarized as follows:

- . Instruction Memory Size up to 4096 12-bit words

- . Data Memory Size up to 4096 8-bit words

- . Tri-State Data bus

- 2k direct addressing of Instruction Memory

- . 1k direct addressing of Data Memory

- 24Ø nanosecond instruction time (full cycle) assuming all bipolar memory

- . Single clock cycle (1 state) per full instruction cycle

- . 6 Registers

- . All modes of 8-bit ALU under software control

- . Easy interchange and intermix of memory types and speeds within the same processor

- . Both parallel and serial I/O capability

- . 16 level automatic push down stack for routine linkage

- . Comprehensive instruction set. (49 basic one word instructions plus 43 arithmetic and logic instructions)

- . TTL Integrated Circuitry

- . Operating Temperature  $\emptyset^{\circ}C$  to  $7\emptyset^{\circ}C$  or  $-55^{\circ}C$  to  $125^{\circ}C$  depending upon grade of IC's used.

The microprocessor executes one complete instruction during one cycle of the basic timing clock. There are no sub-cycle time slots, or states, used within the basic instruction cycle. Consequently, the power of the individual instructions are somewhat less than those of a higher level processor, such as a "minicomputer". However these higher level instructions are available by writing "micro-programs" or "micro-routines" and give the flexibility of, in effect, writing an instruction set in addition to writing higher level routines.

#### 1.1. Physical Configuration

The basic AES microprocessor is contained in one AES modular system unit. The MSU is a standard package configuration with the capability of containing 9 plug in cards. All cards are 7.00" x 7.35" and spaced 0.6" apart. The cards are interconnected either by an artwork or by a wire-wrap backplane. The microprocessor MSU contains the following cards:

- 1) Timing Generator

- 2) Control Logic A

- 3) Control Logic B

- 4)  $1024 \times 8$  Data Memory (RAM)

- 5) 2048 x 12 Instruction Memory (ROM)

Most configurations leave a slot reserved for a maintenance and control interface card that interfaces the microprocessor to a program development and control console, thus enabling the operator to monitor and/or control the microprocessor during maintenance, test or programming.

The remaining 3 positions can be used for a variety of functions. For example if more ROM or RAM capability is required, then a combination of these cards can be inserted into the remaining positions.

Another slot may be reserved for the serial Input/Output control card. There are two versions of this card. In the simpler version the I/O address select, data and control lines are all TRIstate\* outputs and inputs. The more complex version of the I/O card is identical to the simpler one in all respects except that differential line drivers and receivers are used in place of the TRI-state logic. The latter card, whose primary purpose is increasing the allowable load on the I/O bus, is used in cases where the I/O bus is longer than 20 ft and/or when more than 5 I/O channels are used. The remaining two slots may be filled by two parallel I/O interface cards, or 1 interface card and one parallel I/O buffer expander. The parallel I/O buffer card is meant (as in the case of the complex serial I/O card) for increasing the allowable I/O bus loading.

The ROM memory card may be removed and in its place a ROM simulator interface card inserted. This card is used to interface the microprocessor to a ROM simulator which is a part of the program development and control console. The ROM simulator, which is actually a fast bipolar random access memory, behaves exactly as a ROM card where the microprocessor is concerned. It is, however, possible to write instructions into the ROM simulator via an ASR 33 TTY, or a tape reader, thus enabling the programmer to develop and verify the final software before masking the program into the Read Only Memory.

#### 1.2. System Organization

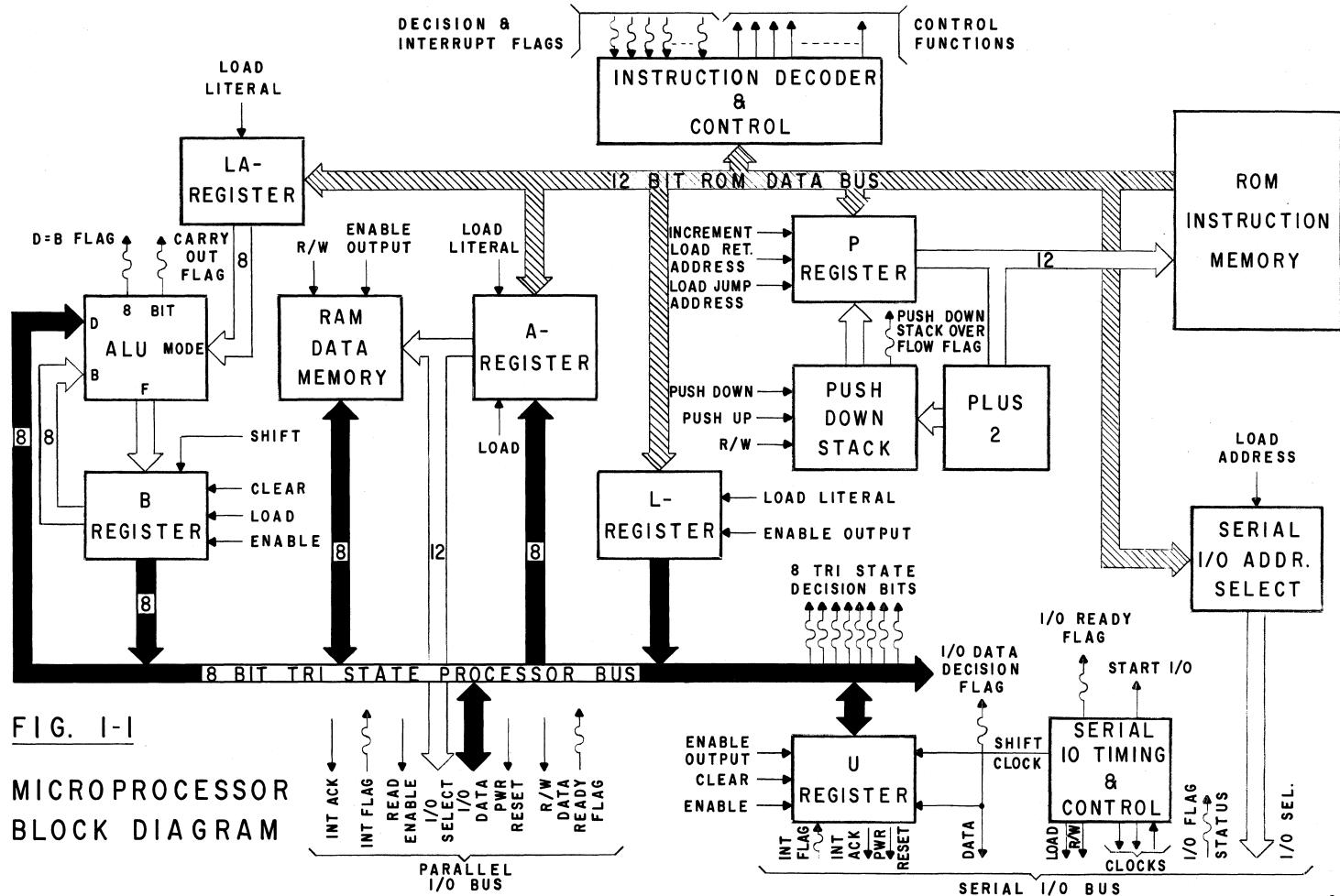

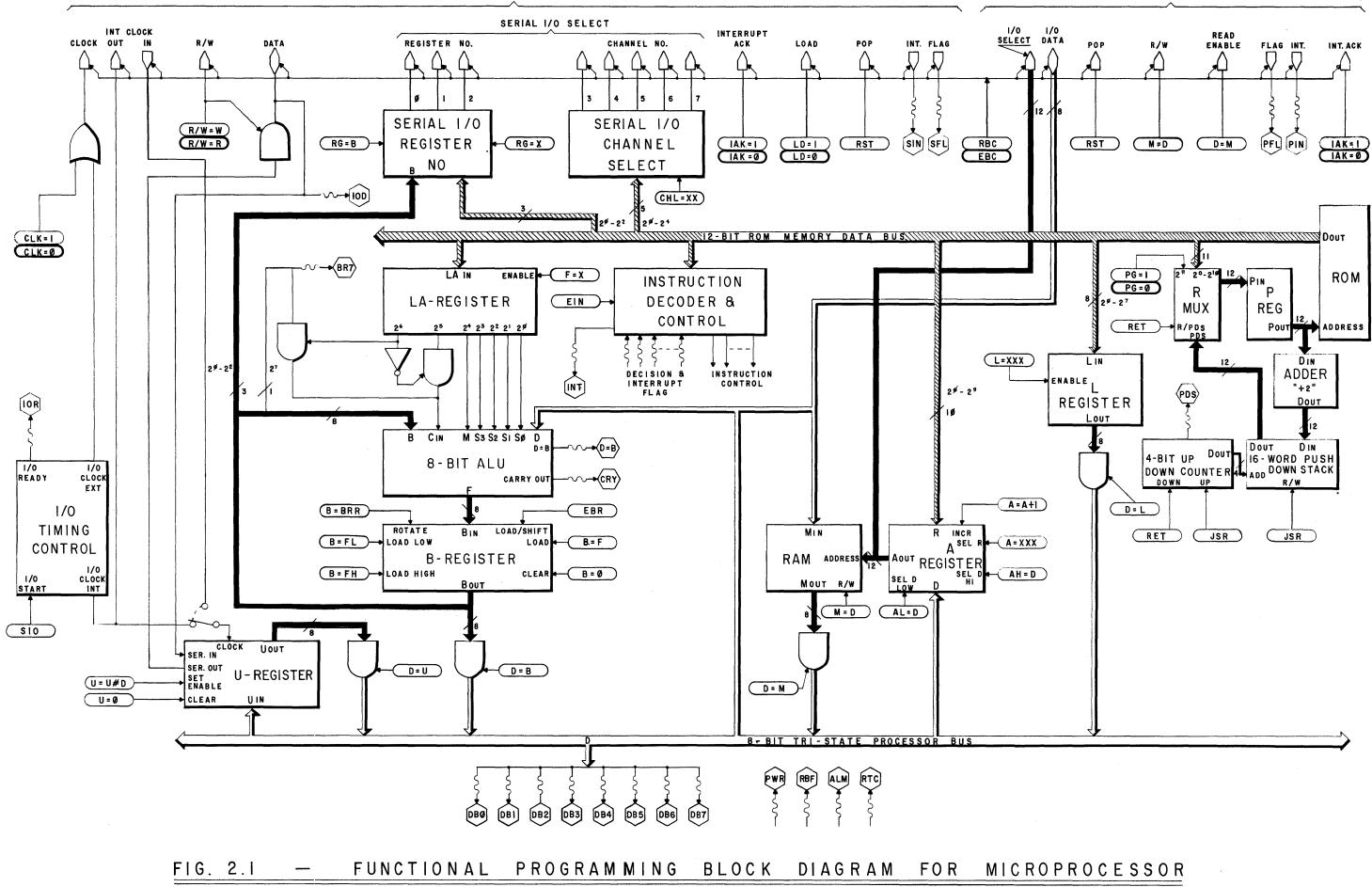

The AES microprocessor is a bus organized machine designed around a data transfer concept. An 8-bit TRI-state processor bus is used as the main highway for data traffic between registers and data memory. The source and destination of data travelling along the processor bus is under complete microprogram control. The basic microprocessor elements are shown in the block diagram of Figure 1-1.

#### 1.3. Instruction Memory

Commands from the read-only instruction memory control all aspects of the microprocessor operation and all commands are executed in a single machine clock cycle. The l2-bit data from the ROM output bus is fed to an instruction decoder, the output of which determines the logic functions to be performed within the processor during the machine cycle. The ROM data bus also goes to the inputs of various registers within the microprocessor so that, depending

\* National Semiconductor Corp. TM.

2.

upon the particular instruction decoded, literal data can be outputted directly from ROM.

#### 1.4. Data Memory

The Data Memory is available with from 1 to 16 256 word by 8-bit modules for a maximum capacity of 4096 words. These modules can be selected from any of the following types and intermixed within the same processor.

Type 1 High speed parallel bipolar scratch pad memory. This type of 256 word memory module has a cycle time faster than the basic machine cycle time of  $24\emptyset$  nanoseconds. Thus data can be read out of or written into this memory during a single machine clock cycle.

Type 2 Non volatile random access read/write core memory module. This type of memory module has a cycle time of 1 micro-second.

Type 3 MOS static random access read/write memory module. This module is partially powered by a rechargeable battery for standby power applications so that the memory remains non volatile for up to 48 hours after external power is removed.

Type 4 Bipolar read only memory module.

Type 5 Special purpose function modules.

As can be seen from figure 1-1, data is both read out of and written into data memory via the high speed 8-bit Tri-State processor bus. Thus, for real time applications, where time is at a premium, memory modules of type 1 should be used because of its speed. This type of memory module also satisfies the need for high speed general storage and working registers.

Memory module types 2 or 3 should be used in cases where momentary power failure can occur but where it is necessary to retain data stored into data memory prior to the power off condition.

Bipolar ROM modules may be used within the data memory bank for storing constants and other predefined data which will never be altered during a program.

Special purpose hardware options such as hardware multiply or fast parallel I/O may also be accommodated by using preselected Data memory address slots. This will be more fully explained in sections  $1.1\emptyset$ ,  $3.\emptyset$ , 3.3 and 3.4.

#### 1.5. Arithmetic Logic Unit (ALU)

The arithmetic logic unit operates on two 8-bit variables the tri-state processor bus and its own output buffer accumulator. The ALU is capable of performing up to 16 logic operations on its two input variables and a variety of arithmetic operations; the most important being add and subtract. The mode of the ALU is selected by the ALU command register which is set by executing a single ALU literal instruction.

#### 1.6. Registers

1.6.Ø. P-Register: The 12-bit P (Program Counter) register indicates the address of the next instruction to be fetched out of instruction memory. The P-register automatically increments by one after the execution of each instruction except in the following cases. If the previous instruction was one of the following:

- a conditional branch instruction whose jumping criteria has been met,

- an unconditional jump instruction, or

- a jump to subroutine instruction, the least significant 11 bits of the P register are loaded with the ROM output data, thus defining the current page jump address. Similarly if the previous instruction was a return from subroutine instruction, the P-register is loaded with the return address last stored into the push-down stack.

1.6.1. A-Register: The 12-bit A (Data Memory Address) register holds the address of the data memory cell being read from or written into. During a RAM address command, its contents may be altered and the l -bit operand field of the instruction loaded into the least significant l bits of the A register.

In addition, three instructions alter the A-register so that:

- the contents of the A register may be incremented,

- the least significant 8 bits of the A register may be loaded with the data present on the TRI-state processor bus, or

- the most significant 4 bits of the A register may be loaded with the 4 least significant bits of the processor bus.

1.6.2. L-Register: The 8-bit L (Literal) register is loaded with the 8-bit literal field of a literal data instruction. If the output of the L register is enabled, an 8-bit literal is available on the processor bus.

4.

1.6.3. LA-Register: The 8-bit LA (ALU Command) register is similar to the L-register in that an 8 bit literal from ROM is loaded into it during an ALU literal instruction. The output of the LA-register selects the operating mode of the ALU.

1.6.4. B-Register: The 8-bit B (ALU Output Buffer) register is the ALU accumulator in which all results of the arithmetic and logical operations are stored. Using the appropriate instructions, the B register may be:

- a) partially loaded by the 4 least significant bits of the ALU output,

- b) partially loaded by the 4 most significant bits of the ALU output,

- c) completely, loaded by all 8 output bits of the ALU,

- d) rotated right by one bit, or

- e) cleared.

1.6.5. U-Register: The U (Universal) register is an 8-bit parallel in, parallel out, serial in or serial out register. It is primarily used as the serial I/O buffer register. To output an 8-bit character onto the serial I/O data bus, data is loaded into the U register from the TRI-state processor bus. When an I/O output command is initiated, the data from the U-register is automatically shifted out onto the I/O data bus. The data is also recirculated back into the U-register so that the character can be retransmitted if necessary. To input a character from the I/O data line, an input command is initiated and the 8-bit character is automatically shifted into the U-register. Appropriate instructions permit the U register to be merged (inclusive "OR" ed) with the data on the TRI-state processor bus, and also to be cleared.

The U-register is also a temporary storage buffer of data on the TRI-state processor bus. It is commonly used as a temporary storage for one byte of a 2 byte address pointer (2 word indirect address) from data memory.

#### 1.7. Decision Flags

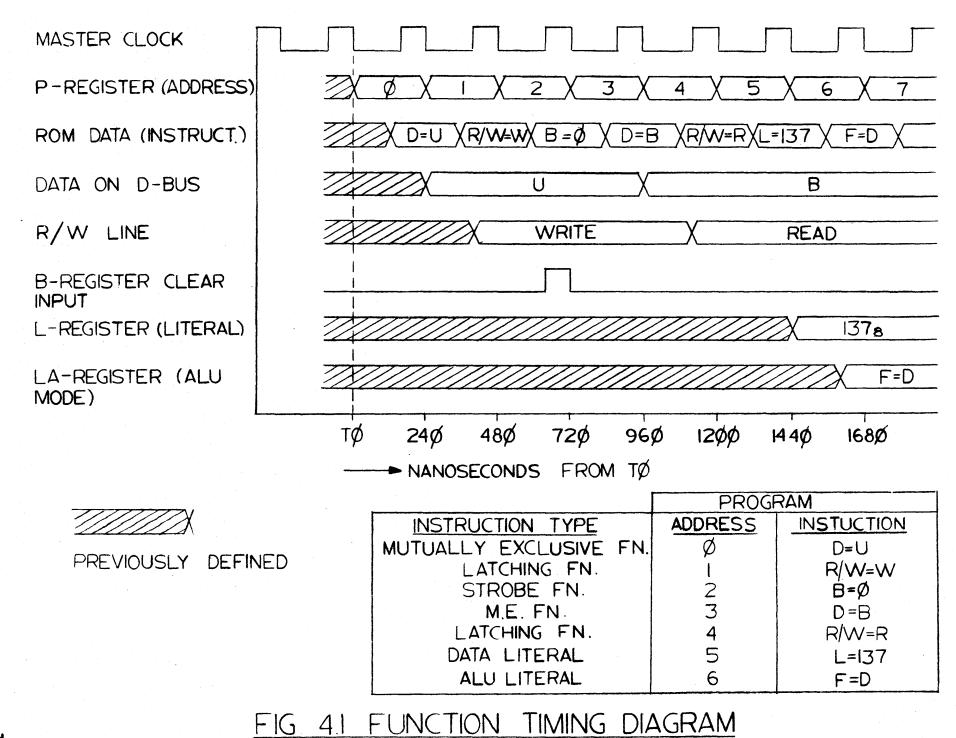

Within the microprocessor there are various status flag bits which are addressed by the appropriate decision instruction. These decision flags are tested by the microprogram to determine whether (or not) a conditional branch operation is implemented. If the decision instruction is decoded, for example, as "branch if decision flag 5 = logic 1", the next instruction will be interpreted as a jump address, or ignored, depending upon whether the decision flag was logic "1" or logic " $\emptyset$ " respectively. Each decision flag may be tested for a logic "1" or a logic " $\emptyset$ " condition permitting the use of both branch if " $\emptyset$ " and branch if "1" instructions.

#### 1.8. Push Down Stack

The AES microprocessor has a 16 level automatic push down stack which is used for routine linkage. When a jump to subroutine command is read from the instruction memory, the contents of the P register plus "2" is stored into the push down stack as a return address to be used when returning from the subroutine. After the return address is stored, the stack is virtually pushed down so that a lower level return address may be stored. This occurs when the subroutine itself calls up yet another subroutine. The next instruction will then automatically be interpreted as a jump address defining the starting location of the subroutine. When a return from subroutine command is read from ROM, the return address will be transferred to the P register from the push down stack during the next machine cycle. When an overflow (e.g. greater than 16 subroutine levels) or an underflow occurs in the push down stack, a decision flag is set.

#### 1.9. Instruction Timing

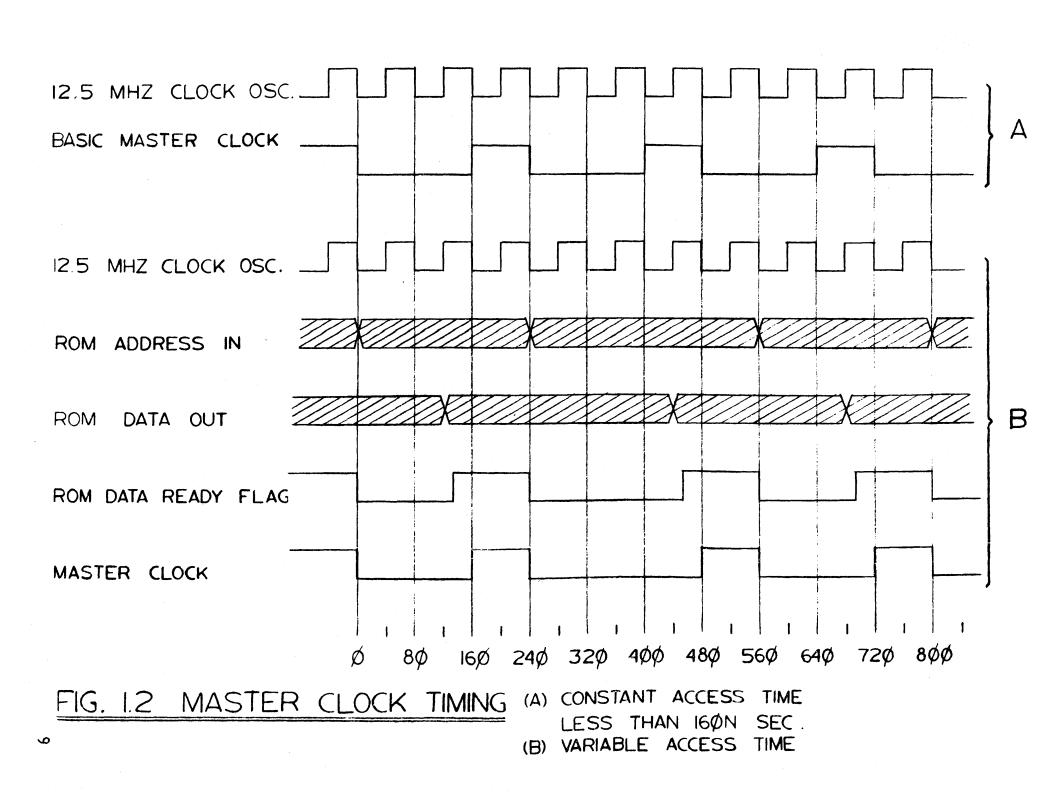

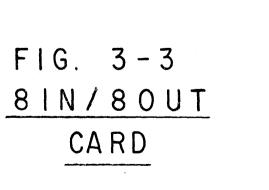

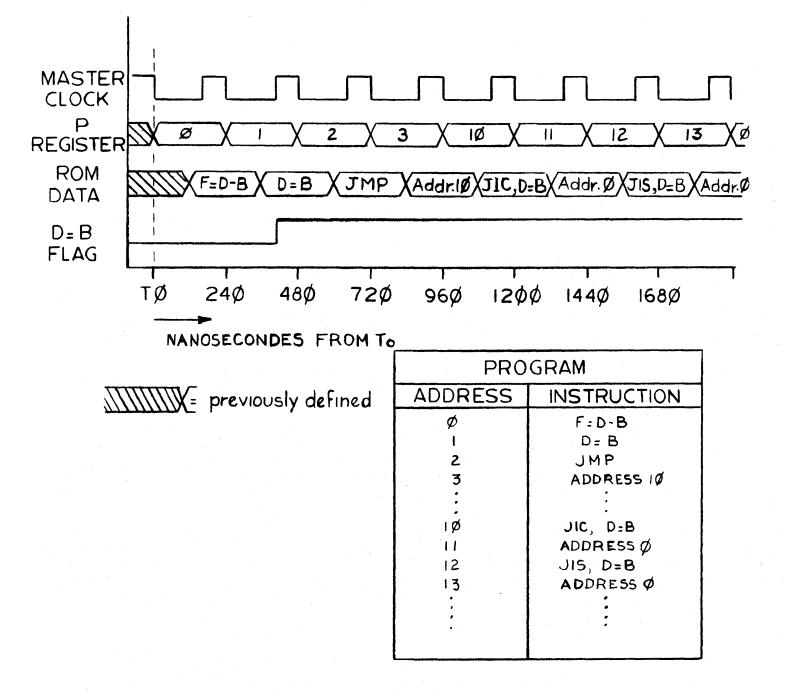

The basic clock is a 12.5 MHz crystal oscillator. The frequency of this oscillator is divided down by 3, producing the microprocessor master clock. This clock has a pulse width of 8Ønano-sec. and a total period of 240 nano-sec. as shown in Fig. 1.2. This period forms the basic machine cycle time and all instructions are executed within this time slot. In some cases, where the instruction or data memory has an access time longer than 160 n sec, a memory ready flag from the memory device being accessed may be used to lengthen or delay the master clock in increments of 80 nano-This feature of having a variable cycle time is normally not sec. used. It does, however, provide the flexibility of intermixing both slow and fast memory types within the same microprocessor without completely slowing down the master clock to accommodate the slowest memory module. It should be noted that only the leading and trailing edges of the master clock pulse are used for strobing or setting the various logic functions throughout the control logic of the microprocessor. No other sub-clocks delay lines or one-shots are used for timing purposes. When the P register is incremented or loaded, the new instruction address is available. After the memory access time has been reached, data is available for instruction decoding. Both the leading and trailing edges of the next clock pulse are used for executing the instruction just read. The detailed timing diagrams for the various instructions are provided in section IV.

#### 1.1Ø. Input/Output Interface

The AES microprocessor I/O interface provides the necessary timing and control to communicate with both low and high speed peripheral devices. The serial or low speed I/O bus consists of 8 address lines, (defining the peripheral device address), one read/write line, one load strobe line, 3 I/O clock lines, one flag status line, one interrupt flag, one interrupt acknowledge line and one serial data line. This I/O bus is used to transfer 8 bit serial characters into or out of the microprocessor at rates up to one character every 9.12 micro-seconds.

As soon as the selected peripheral has been addressed, and the data to be transferred is ready either in the U-register (for transmitting) or on the addressed I/O device (for receiving), a start I/O instruction is executed. The clocking and transfer of I/O data then becomes automatic, with the microprocessor free to execute other instructions during the I/O interval. As soon as the I/O transfer is complete, the I/O ready decision flag is set. This enables the microprocessor to branch when I/O is complete. In addition to the serial I/O, a parallel I/O capability is available. This is normally used as a means of providing hardware processor options such as hardware multiply/divide or sine/cosine function hardware etc.

This bus is also used as a means of accessing a large data base such as a disc or magnetic tape unit, where maximum data throughput is necessary.

The parallel I/O bus consists of 12 address lines, 8 I/O data lines, a write strobe, a read enable line, an interrupt flag, a device ready flag and an interrupt acknowledge line. The I/O address and data lines are the same as those used for accessing the microprocessor data memory, i.e. the 8 bit TRI-state processor bus is the same as the I/O data bus, and the A-register outputs are also the 12 addressing lines for the parallel devices. A power reset pulse is sent to all peripherals both on the serial and parallel I/O bus when the power on reset condition is present.

A more detailed description of both the serial and parallel I/O structure is given in section III.

7.

#### II. Micro-Instruction Repertoire

The AES micro-processor has 92 basic one-word instructions, all executable in 240 nanoseconds. This section describes all of these micro-instructions. With each description is a diagram showing the format of the command, the mnemonic used in referencing it and also the two character ASCII code. The latter is used as the binary paper tape format when loading the ROM simulator via an ASR 33 TTY or paper tape reader.

#### 2.Ø. Instruction Formats

There are six basic instruction formats. Each microinstruction is 12 bits in length and is contained in a single read-only memory location.

The formats are for function, decision, ROM address, RAM address, Data Literal and ALU literal micro-instructions.

#### 2.Ø.Ø. Function

The function micro-instructions have the following format:

| ø  | ø  | ø | 1, | s/c | 2 | FUNC | TIC | DN S | SELE | CT |   |

|----|----|---|----|-----|---|------|-----|------|------|----|---|

| 11 | 1Ø | 9 | 8  | 7   | 6 | 5    | 4   | 3    | 2    | 1  | ø |

The function type of micro-instruction is used for setting or clearing various control signals within the machine. The simplest type of function is a latching function. In this case, execution of the instruction implies setting or clearing the logic signal defined by the function select code, depending upon whether bit 7 is a 1 or a  $\emptyset$  respectively. The second type of function is a strobing function. This type of instruction sets the addressed function line for one machine cycle period only. This type of function is used for strobing latches and clocking registers etc. Bit 7 is not decoded in this case.

The third type is a mutually exclusive function. The setting of one function within a mutually exclusive group also implies the clearing of all other functions within that group. If one mutually exclusive function is cleared, all functions within that group will also be cleared.

The last type of function is a strobe, branch type of instruction. This behaves like a strobe function, but in addition the next instruction is unconditionally treated as a branch address. The only function of this type is the jump to subroutine instruction explained in section 2.11.

#### 2.Ø.1. Decision

The decision micro-instruction has the following format.

| ø  | ø  | ø | ø | s/c | DE | CIS | ION | SE | LEC | т |   |

|----|----|---|---|-----|----|-----|-----|----|-----|---|---|

| 11 | 10 | 9 | 8 | 7   | 6  | 5   | 4   | 3  | 2   | 1 | ø |

10.

When bits 8-11 of the micro-instruction are  $\emptyset$ , the first seven bits form a selection address to interrogate one of 27 possible decision flags. If the flag is equal to the value of bit 7, the next micro-instruction will be treated as a branch address.

#### 2.Ø.2. ROM Address

The ROM address micro-instruction has the following format:

| 1  |    | CU | RRE | NT | PAG | ER | ОМ | ADD | RES | S |   |

|----|----|----|-----|----|-----|----|----|-----|-----|---|---|

| 11 | ıø | 9  | 8   | 7  | 6   | 5  | 4  | 3   | 2   | 1 | ø |

The ROM address micro-instruction is defined by a l in bit ll. After the execution of a valid decision or a strobe branch function, the least significant ll-bits of the next word of memory data coming from ROM is loaded into the P register. Bit ll of the P register remains unchanged, A ROM address command located anywhere else in a micro-program is ignored. The combination of a decision followed by a ROM address can be thought of as a two word conditional branch instruction.

#### 2.Ø.3. RAM Address

The RAM address micro-instruction has the following format:

| ø  | 1  | CU | RRE | NT | PAG | ΕF | RAM | ADD | RES | S |   |

|----|----|----|-----|----|-----|----|-----|-----|-----|---|---|

| 11 | 10 | 9  | 8   | 7  | 6   | 5  | 4   | 3   | 2   | 1 | ø |

When bits ll and 10 are 0 and l respectively, the remaining bits are stored into the least significant 10-bits of the A register. Bits 10 and 11 of the register are left unchanged.

#### 2.Ø.4. Data Literal

The Data Literal address micro-instruction has the following format:

| Ø  | ø  | 1 | ø |   | 1 | LI | TER | AL | .1 | 1 |   |

|----|----|---|---|---|---|----|-----|----|----|---|---|

| 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4   | 3  | 2  | 1 | ø |

When bits 11, 10, 9 and 8 are 0, 0, 1 and 0 respectively, the 8 bit literal, defined by bits 0-7, is stored into the L-register.

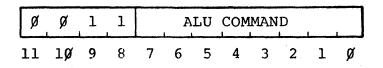

#### 2.Ø.5. ALU Literal

The ALU Literal address micro-instruction has the following format:

In a similar fashion to the data literal micro-instruction, the ALU literal command enables the 8 bit literal defined by bits  $\emptyset$ -7 onto the LA register.

#### 2.1. Terms, Mnemonics and Symbols

The AES microprocessor's instruction memory consists of 12-bit words. For convenience of programming, entering data, printing out, and preparing punched paper tape, the 12 bits are organized into two modified ASCII characters of 6 bits each. These characters are a subset of the USA Standard Code for Information Interchange (USASCII). A conversion table between 6 bit binary to 2 number octal to ASCII is given in Appendix 1. To use this table , the 12 bit instruction is split into two 6 bit characters. The modified ASCII representation of the instruction is simply the most significant 6 bit character followed by the least significant character represented in modified ASCII. For example:

The modified ASCII representation of the following function

| Ø  | ø  | ø | 1 | 1 | ø | ø | ø | ø | 1 | 1 1 |

|----|----|---|---|---|---|---|---|---|---|-----|

| 11 | 1ø | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 Ø |

is FG.

Some of the symbols and terms used in the description of instructions are:

| <sup>A</sup> 1 <sup>=A</sup> 2 | Set contents of $A_1$ equal to $A_2$ . $A_2$ is left unchanged. |

|--------------------------------|-----------------------------------------------------------------|

| JIS,xxx                        | Jump if flag xxx is set.                                        |

| JIC,xxx                        | Jump if flag xxx is clear.                                      |

| #                              | Logical OR operation.                                           |

| •                              | Logical AND operation.                                          |

| ↑<br>•                         | Logical EXCLUSIVE OR operation.                                 |

| A'                             | Logical Complement of A.                                        |

| +                              | Arithmetic plus operation.                                      |

|                                | Arithmetic minus operation.                                     |

The rest of section II is devoted to describing the AES Microprocessor instructions. The detailed functional programming block diagram shown in Fig. 2.1. may be used as a guide in understanding these commands.

- 2.2.

- Load Data Bus Instructions

| Mnemonic | ASCII | Description                                    |

|----------|-------|------------------------------------------------|

| D=L      | F@    | Load data bus with contents of the L-register. |

| D=M      | FA    | Load data bus with data memory output.         |

| D=U      | FB    | Load data bus with contents of the U-register. |

| D=B      | FC    | Load data bus with contents of the B-register. |

These four instructions form a mutually exclusive function set.

2.3.

Load Literal Buffer Instruction

| Mnemonic              | ASCII                | Description                                                                                                                     |

|-----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| $L = \underline{xxx}$ | Hoc.<br>Ioc.<br>Joc. | Load L-Register with octal number $\frac{xxx}{\cancel{0}}$ (xxx may take on the values $\frac{\cancel{0}}{\cancel{0}}$ - 3778). |

|                       | K .c.                | ∞ will be one of the 64 ASCII characters listed in Fig. 2.1.                                                                    |

#### 2.4. ALU Mode Instructions

This group comprises the instructions for performing logical and arithmetic operations on two 8-bit quantities namely D (8 bit processor data bus) and B (B-register output), and providing an 8 bit quantity as an output, termed F. This output may be stored into the B register by using the appropriate instruction. The ALU mode of instructions may further be subdivided into the following groups.

#### Loading Instructions

| Mnemonic | ASCII , | Description                                                                                 |

|----------|---------|---------------------------------------------------------------------------------------------|

| F=D      | L@      | Set the ALU output equal to the data bus.                                                   |

| F=D'     | LP      | Set the ALU output equal to the complement of the data bus.                                 |

| F=B      | LZ      | Set the ALU output equal to the B-register output.                                          |

| F=B '    | LU      | Set the ALU output equal to the complement of the B-register output.                        |

| F=-1     | LC      | Set the ALU output equal to<br>minus 1 (2's complement), i.e.<br>all bits of F are logic 1. |

| F=Ø      | LS      | Set all bits of the ALU output to logic $\emptyset$ .                                       |

### Logic Instructions

| Mnemonic | ASCII | Description                                                                       |

|----------|-------|-----------------------------------------------------------------------------------|

| F=D#B    | LA    | Set the ALU output equal to the logical or of D and B.                            |

| F=D#B'   | LB    | Set the ALU output equal to the logical or of D and $\overline{B}$                |

| F=D'#B   | ΓX    | Set the ALU output equal to the logical or of $\overline{D}$ and B.               |

| F=D'#B'  | LT    | Set the ALU output equal to the logical or of $\overline{D}$ and $\overline{B}$ . |

| F=D.B    | L [   | Set ALU output equal to the logical and of D and B.                               |

| F=D.B'   | TM    | Set ALU output equal to the logical and of D and $\overline{B}$ .                 |

| F=D'.B   | LR    | Set ALU output equal to the logical and of $\overline{D}$ and B.                  |

| F=D'.B'  | LQ    | Set ALU output equal to the logical and of $\overline{D}$ and $\overline{B}$ .    |

| F=D↑B    | LV    | Set ALU output equal to the exclusive or of D and B.                              |

| F=D↑B'   | LY    | Set ALU output equal to the exclusive or of D and $\overline{B}$ .                |

#### Arithmetic Instructions

| Mnemonic | ASCII     | Description                                                       |          |

|----------|-----------|-------------------------------------------------------------------|----------|

| F=D+D    | ΓΓ        | Set ALU output equal to D.                                        | o D plus |

| F=D+B    | LI        | Set ALU output equal to B.                                        | o D plus |

| F=D+D+1  | L,        | Set ALU output equal to<br>D plus l.                              | o D plus |

| F=D+B+1  | <b>L)</b> | Set ALU output equal to<br>B plus 1.                              | o D plus |

| F=D-B    | L&        | Set ALU output equal to<br>B. (negative numbers a<br>complement). |          |

| Mnemonic     | ASCII         | Description                                   |   |

|--------------|---------------|-----------------------------------------------|---|

| F=D-B-1      | LF            | Set ALU output equal to D minus<br>B minus l. |   |

| F=D+1        | L(space)      | Set ALU output equal to D plus 1.             |   |

| F=D-1        | LO            | Set ALU output equal to D minus 1             | • |

| Combined Log | ical and Arit | hmetic Instructions                           |   |

In the following group of instructions, it is assumed that logical operations are done before the arithmetic ones.

| Mnemonic          |              | ASCII                                                                                          |                                |

|-------------------|--------------|------------------------------------------------------------------------------------------------|--------------------------------|

| F=D#B+D           |              | LM                                                                                             |                                |

| F=D#B <b>'</b> +D |              | LN                                                                                             |                                |

| Mnemonic          | ASCII        | Mnemonic                                                                                       | ASCII                          |

| F=D#B+1           | L!           | F=D#B'+1                                                                                       | L"                             |

| F=D#B+D+1         | L-           | F=D#B'+D+1                                                                                     | L.                             |

| F=D.B+D           | LH           | F=D.B'+D                                                                                       | LD                             |

| F=D.B+D+1         | L (          | F=D.B'+D+1                                                                                     | L\$                            |

| F=D.B-1           | LK           | F=D.B'-1                                                                                       | LG                             |

| F=D#B+D.B'        | LE           | F=D#B'+D.B                                                                                     | LJ                             |

| F=D#B+D.B'+1      | L%           | F=D#B'+D.B+1                                                                                   | L*                             |

| Shift Rotate      | Instructions |                                                                                                |                                |

| Mnemonic          | ASCII        | Description                                                                                    |                                |

| F=BSL             | LL           | Set the ALU outputhe B-register shift. The LSB of is set to $\emptyset$ .                      | ifted left one                 |

| <br>F=BRL         | ML           | Set the ALU outpu<br>the B register ro<br>bit. Thus the LS<br>output is equal t<br>B-register. | tated left one<br>B of the ALU |

| EBR               | N@           | Set the B-registe rotate mode.                                                                 | r into the                     |

The first two shift rotate instructions require that the Bregister is enabled onto the data bus (D=B Is the last load data bus instruction to be executed).

| Mnemonic | ASCII | Description                                                                                                                                                 |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B=∅      | РН    | Clear the accumulator or B-<br>register.                                                                                                                    |

| B=F      | FI    | Load the B-register with the output of the ALU.                                                                                                             |

| B=FH     | FJ    | Load the B-register's most<br>significant 4 bits with those<br>of the ALU output. The least<br>significant 4 bits of the B<br>register are left unchanged.  |

| B=FL     | FK    | Load the B-register's least<br>significant 4 bits with those<br>of the ALU output. The most<br>significant 4 bits of the B-<br>register are left unchanged. |

| B=BRR    | FI    | Rotate the B-register right on bit.                                                                                                                         |

These instructions all fall under the category of strobe functions. The last preceding ALU Literal command before a B=BRR instruction must be EBR. On the other hand, the last preceding ALU Literal before B=F, B=FH or B=FL must not be EBR.  $B=\emptyset$  will clear the accumulator in both cases.

| 2.6. | RAM Address In | structions   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Mnemonic       | ASCII        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | A= <u>xxx</u>  | <i>∝ /</i> 3 | Load A register with address<br><u>xxx</u> ( <u>xxx</u> is the 10 bit RAM<br>address and may take on the<br>values $\emptyset - 1777_8$ ).<br>Depending on the address chosen, $\alpha$<br>will be one of the following<br>ASCII characters:<br>(P, Q, R, S, T, U, V, W, X, Y,<br>Z,[,], $\uparrow$ , or $\leftarrow$ ) and $\beta$ will<br>be one of the 64 ASCII characters<br>listed in Appendix 1. Bits 10<br>and 11 of the A-register are left<br>unchanged. |

|      | AL=D           | FE           | The data bus is loaded into the<br>8 least significant bits of the<br>A-register. Bits 8, 9, 10 and<br>11 of the A-register are left un-<br>changed.                                                                                                                                                                                                                                                                                                              |

|      | AH=D           | FF           | Bits 8, 9, 10 & 11 of the A-<br>register are loaded with bits                                                                                                                                                                                                                                                                                                                                                                                                     |

17.

2.5.

$\emptyset$ , 1, 2 & 3 of the data bus respectively.

A=A+1 F:

Increment the contents of the A-register.

#### 2.7 Store Into RAM Instruction

| Mnemon | ic |

|--------|----|

|        |    |

ASCII

$\mathbf{FL}$

M=D

#### Description

Load data bus into RAM. The address in RAM must be previously defined by a RAM address instruction. The data memory is normally in the read mode and the M = D instruction, which is a strobe function, sends a write pulse to the RAM for the duration of the machine cycle.

#### 2.8. Conditional Branch Instructions

This group comprises the instructions that direct the program to a nonsequential address for execution of the instruction located there. As previously shown in section  $2.\emptyset.1$ , bits  $\emptyset$  to 6 of the ROM data define which of the possible 27 decision flags will define the logical condition for execution of the jump. The jump address is contained in the next word from instruction memory. Each of the following branch instructions comes in complementary pairs, i.e. jumping when the decision flag is either set or cleared.

| Mnemonic                                                                             | Mnemonic<br>for<br>Complement                                                        | ASCII                                        | ASCII<br>for<br>Complement             | Description                                                                                                                                                                |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JIS, <sub>BR7</sub>                                                                  | JIC,BR7                                                                              | BC                                           | @C                                     | Jump if B-register bit<br>7 is Set/Clear.                                                                                                                                  |

| JIS,CRY                                                                              | JIC,CRY                                                                              | BD                                           | @D                                     | Jump if ALU carry output<br>flag is Set/Clear. This<br>flag is a "1" when there<br>is an overflow or under-<br>flow during an ALU addition<br>or subtraction respectively. |

| JIS,D=B                                                                              | JIC,D=B                                                                              | BE                                           | @E                                     | Jump if data bus and B-<br>register are equal/not<br>equal. ALU must be in<br>F=D-B-1 mode. (see pg.16).                                                                   |

| JIS,DBØ<br>JIS,DB1<br>JIS,DB2<br>JIS,DB3<br>JIS,DB4<br>JIS,DB5<br>JIS,DB6<br>JIS,DB7 | JIC,DBØ<br>JIC,DB1<br>JIC,DB2<br>JIC,DB3<br>JIC,DB4<br>JIC,DB5<br>JIC,DB6<br>JIC,DB7 | BH<br>BI<br>BJ<br>BK<br>BL<br>BM<br>BN<br>BO | 0H<br>0J<br>0K<br>0L<br>0M<br>0N<br>00 | Jump if bit n of the data bus is set/clear where $n = \emptyset$ to 7                                                                                                      |

MnemonicMnemonicASCIIASCIIDescriptionforforforComplementComplement

JIS, PDS

JIC,PDS BW

Jump if push down stack overflow flag is Set/ Clear. This flag is set when the 16 levels of push down stack are either overflowed or underflowed. It is automatically cleared when the microprocessor is in the PORC condition. Thus, a reset instruction will clear it. (see pg. 22).

The remaining conditional branch instructions are described in the section on Input/Output.

@W

#### 2.9. Set Page Instructions

As shown in Section 2. $\emptyset$ .2, the least significant ll-bits of a ROM address instruction enables the direct addressing of 2 $\emptyset$ 48 memory locations. For addressing all the 4 $\emptyset$ 96 locations, the following instructions should be used.

| Mnemonic | ASCII | Description                                                                                                  |

|----------|-------|--------------------------------------------------------------------------------------------------------------|

| PG=∅     | DT    | The most significant bit (bit 11) of the parallel input to the P-register is set to $\emptyset$ . This means |

|          |       | that the next valid decision to take place will cause a jump to                                              |

|          |       | page $\emptyset$ of the instruction memory.                                                                  |

|          |       | The page is always set to $\emptyset$ automatically after power goes on.                                     |

| PG=1     | FT    | Bit ll of the P-register parallel                                                                            |

|          |       | input is set to 1 so that the next branch will be to the upper page                                          |

|          |       | of instruction memory.                                                                                       |

It should be noted that a  $PG_=\emptyset$  or  $PG_=1$  instruction does not change the page at the time of the command, but rather defines the page to be jumped to at the next branch.

2.10. Unconditional Jump Instruction

| Mnemonic | ASCII | Description                                                               |

|----------|-------|---------------------------------------------------------------------------|

| JMP      | B@    | This instruction causes an uncon-<br>ditional jump to the address         |

|          |       | defined by the ROM address pointer                                        |

|          |       | following it and to the page number last set by the set page instruction. |

19.

#### 2.11. Jump to Subroutine Instruction

| Mnemonic | ASCII | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JSR      | FØ    | This loads an address two greater<br>than that in the P register into<br>the push down stack. After this<br>return address is stored, the<br>stack is pushed down ready to<br>accept another return address.<br>The next instruction from ROM<br>will be treated as an uncondi-<br>tional branch address to which<br>the P register will be set.<br>This instruction is a strobe<br>branch function. |

2.12. Return from Subroutine Instruction

| Mnemonic | ASCII | Description                                                                                                                                                                                             |

|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RET      | FN    | This instruction causes the push<br>down stack to "push up", thus<br>revealing the last return address<br>stored into it. This return<br>address is then enabled onto the<br>P register parallel input. |

|          |       | In addition to the next instruction<br>from ROM being executed, the return<br>address will be loaded into the P<br>register causing a return jump to<br>the subroutine calling program.                 |

#### 2.13. NOP and HALT Instructions

| Mnemonic                                                                                                                                             | ASCII                                                                                                   | Description                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP                                                                                                                                                  | @@                                                                                                      | No operation is performed by this instruction except that a one machine cycle delay of 240 n. seconds results.                                                                                                                                                                                                                   |

| HLT=Ø<br>HLT=1<br>HLT=2<br>HLT=3<br>HLT=4<br>HLT=5<br>HLT=6<br>HLT=7<br>HLT=1Ø<br>HLT=11<br>HLT=12<br>HLT=13<br>HLT=14<br>HLT=15<br>HLT=16<br>HLT=17 | F(space)<br>F!<br>F#<br>F\$<br>F\$<br>F%<br>F&<br>F<br>F<br>F(<br>F)<br>F*<br>F+<br>F,<br>F-<br>F.<br>F | If a maintenance and control<br>chassis is interfaced to the micro-<br>processor, any one of the 16 HALT<br>instructions will stop the pro-<br>cessor master clock. In the case<br>where no maintenance and control<br>chassis is connected to the micro-<br>processor all HALT instructions<br>are ignored and treated as NOPs. |

#### 2.14. PORC and the RST Instruction

The PORC or power on reset circuit is used to provide the required hardware initialization when first turning the microprocessor on. When power is first turned on, PORC condition exists within the microprocessor for approximately 100 milli seconds. During this condition the following is done.

- a) The master clock oscillator is disabled from the microprocessor.

- b) The P and A registers are cleared (set to address  $\emptyset$ ).

- c) A power reset pulse is sent to all peripherals both on the serial and the parallel I/O bus.

- d) The instruction memory page function is set to  $\emptyset$ .

- e) The CLK, LD, R/W and RBC functions are all cleared. These functions will be explained in the section on Input/Output.

- f) The interrupt acknowledge function is set to  $\emptyset$ .

- g) The push down stack is set to subroutine level  $\emptyset$  and the overflow PDS flag is cleared.

- h) The master interrupt flag is disabled.

The PORC condition may also be initiated in two other ways. The first way is to press the reset button on the maintenance and control chassis, assuming it is connected to the microprocessor. The second way is to execute a reset instruction.

| Mnemonic | ASCII | Description                                        |

|----------|-------|----------------------------------------------------|

| RST      | F8    | Strobe the microprocessor into the PORC condition. |

#### 2.15. Real Time Clock and the RTC Instruction

The real time clock provides the setting of the decision flag at a crystal-controlled timing rate. The timing is derived from the microprocessor internal master clock which is divided down by some integral number as determined by optional strapping. This clock frequency may be strapped into the master interrupt circuit (see sec. 3.1.) for use in interrupt mode, or may be used as a decision flag to be detected under program control. Although only one decision flag (RTC) is mentioned, more are available as an option.

| Mnemonic | Mnemonic<br>for<br>Complement<br>Instruction | ASCII | ASCII<br>for<br>Complement<br>Instruction | Description                           |

|----------|----------------------------------------------|-------|-------------------------------------------|---------------------------------------|

| JIS, RTC | JIC,RTC                                      | BF    | @F                                        | Jump if real time clock is set/clear. |

SERIAL 1/0 BUS

22

#### III. Input/Output

The AES Input/Output system provides a powerful and flexible interface between the microprocessor and the peripheral devices that are connect to it.

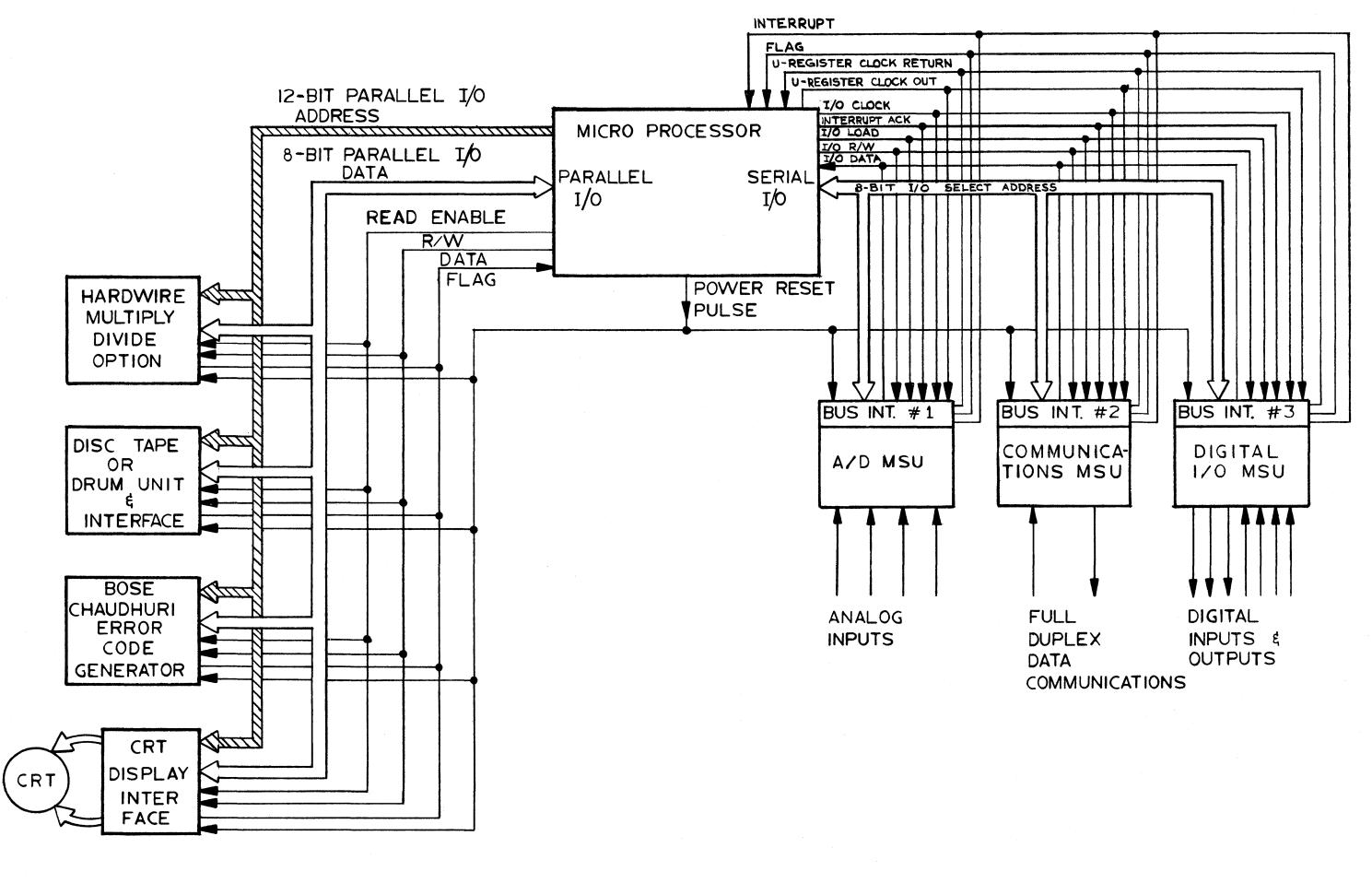

The I/O system may be subdivided into two principal parts namely (a) serial I/O and (b) parallel I/O. A typical I/O system configuration is shown in Fig.3-1.

3.Ø. Serial I/O

#### 3.Ø.1. I/O Bus Structure

The I/O bus that interconnects the microprocessor to the external device has the following structural elements:

- a) Address: 8 lines defining an 8 bit I/O select code for addressing up to 256 8 bit registers. 5 lines are used for defining one of 32 channels and the remaining 3 are used for selecting one of 8 registers within the channel.

- b) Control: 5 lines called LOAD, R/W, CLOCK, IAK and POP. The first three signals control the transfer of data to or from the external device and the fourth signal acknowledge an interrupt request. The POP signal is the power on pulse generated during a PORC condition.

- c) <u>Flags</u>: A status flag corresponding to the I/O select code may be read on one line of the I/O bus. A serial I/O interrupt flag line is also available. This is the logical "OR" of all the interrupt flags within the system.

- d) Data: One bi-directional line is available on the serial I/O bus for transferring 8-bit serial characters to or from the microprocessor.

- e) Propagation Delay: Two additional clock lines exist within the serial bus. This permits the reading of serial data into the microprocessor to be independent of the physical length of the bus. The clock which is used to shift I/O data through the U-register is "transmitted" onto the I/O bus from the microprocessor and "reflected" from the addressed peripheral. The return clock line is then used so shift serial data into the U-register.

Drivers and receivers are contained in the microprocessor and in the external peripherals for signalling over the serial I/O bus. Three options concerning the types of line drivers or receivers are available to the user. Type 1: For simple systems (maximum of 2 I/O channels, proximity of less than 5 ft.), all unidirectional bus lines use standard TTL gates as both drivers and receivers and bi-directional lines use TRI-state \* TTL logic gates as drivers and standard TTL gates as receivers. For this system configuration no serial Input/ Output control card is necessary.

<u>Type 2</u>: For medium sized systems (maximum of 5 I/O channels, proximity of less than  $2\emptyset$  ft.) all bus lines use TTL TRI-state gates for both drivers and receivers. Each signal line is twisted with a ground line to form a twisted pair.

<u>Type 3</u>: For large systems, using more I/O than types 1 and 2, all bus lines make use of "Party Line" differential line drivers and receivers. These drivers are able to drive up to 1000 ft. of bus line at standard TTL speeds.

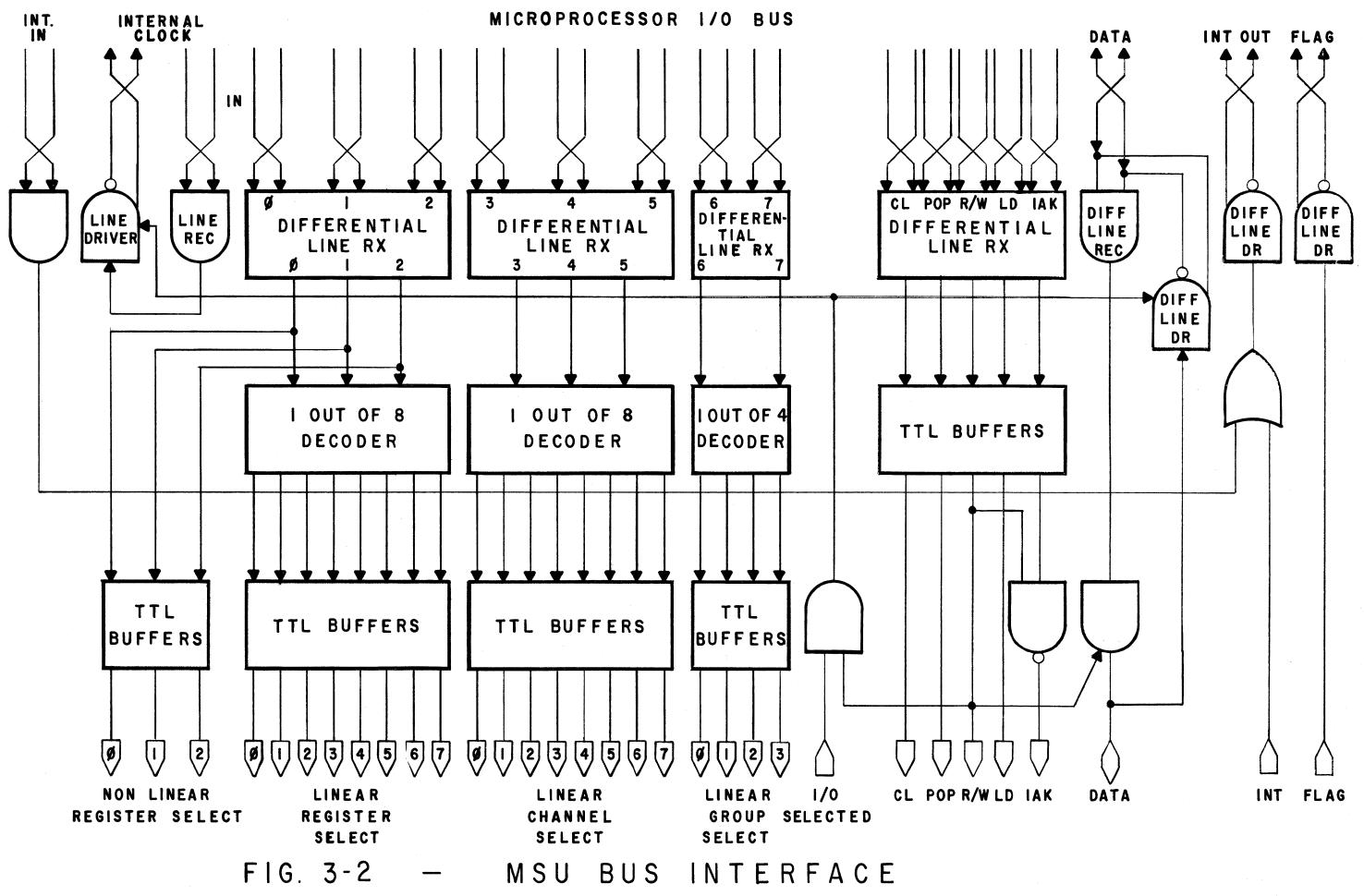

#### 3.Ø.2 Modular System Unit Bus Interface

The modular system unit (MSU) bus interface card is designed to interface up to 8 I/O peripheral interface cards to the microprocessor serial I/O bus (see Fig.3.2). This card is intended for use in systems of type 3 and its primary function is to interface the differential driver and receiver signals to standard TTL logic levels. This card also decodes the eight address select lines to form 4 group.8 channel and 8 register linear select signals for enabling the I/O cards within the modular system unit.

The I/O devices within the MSU provide an I/O selected signal which indicates if one of them has been addressed. When this signal is high, the I/O flag status is enabled onto the I/O bus. When the I/O selected line is high and, in addition, the R/W line is in the read condition, both the data line and microprocessor I/O clock are enabled onto the I/O bus.

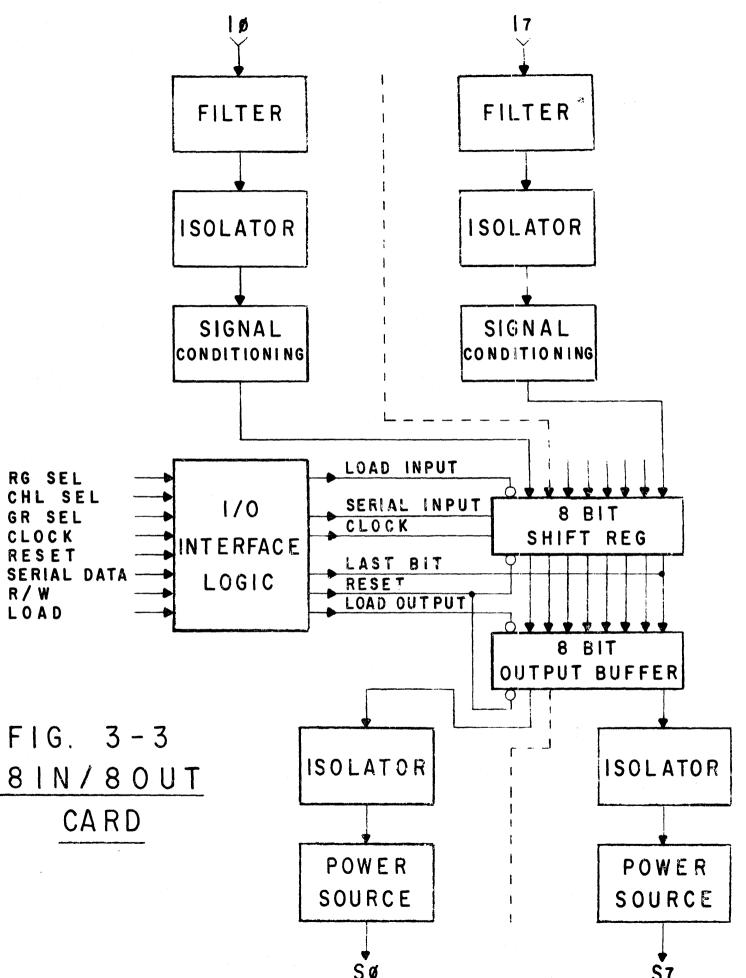

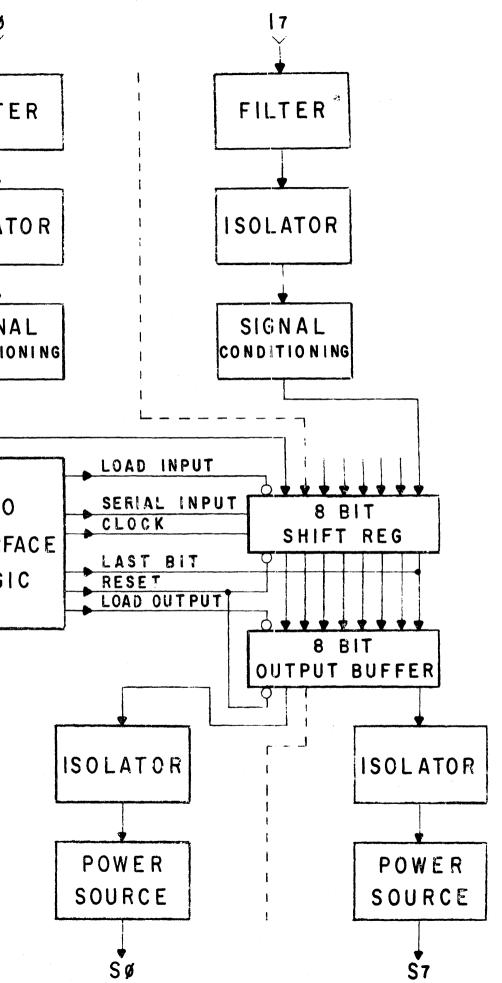

#### 3.Ø.3 Typical I/O Board

A typical MSU module contains 9 I/O cards which communicate with an AES microprocessor through an MSU bus interface card. A typical example of the type of I/O cards is an 8 IN/8 OUT card. The block diagram of such a card is shown in Fig.3-3. The following is a description of the functions of the various block interconnections.

The 8 IN/8 OUT provides the following capabilities:

- 1) Reading status of 8 external points and inputting the information to the microprocessor.

- \* National Semiconductor Corp. TM.

2) Outputting drives (sinks) to 8 external points

The input and output of this information is under complete microprocessor program control.

The block labelled I/O INTERFACE LOGIC provides the media of interpreting microprogrammed sequences as well as decoding the destination address of these sequences. The address decode is a strappable option. Consequently, if a string of commands contains the address of the 8 IN/8 OUT board then READ/WRITE action is initiated depending on the request. For example, if the request is to read status from 8 external points then the 8 points in question are strobed into the 8 BIT SHIFT REGISTER and a second sequence would automatically shift the data onto the serial I/O bus and into the microprocessor. Similarly the outputting of data follows the same pattern.

Several other features are provided for by the card. Consider first the 8 input lines. The status input lines are isolated from the logic with photocoupled isolators. This separates the logic from any power or ground line noise induced on the status lines. Furthermore, each line has an input filter which can protect against induced electrical transients (up to 3.5kV). A third feature is provided in the signal conditioning circuitry. This basically prevents any slowly changing status signals from causing the logic to operate in its linear region. Linear region operation would generate oscillations in the logic.

The output lines are also isolated from the logic and are protected against electrical transients. An important feature for the outputs is the capability of providing either a source of power for the 8 external points or of sinking current from these same 8 sources. This source/sink capability is an option on the card.

#### 3.Ø.4 Serial I/O Interrupt

All I/O interface cards within a Modular System Unit having an interrupt flag, output this signal which is logically "OR" ed within the MSU to form the interrupt flag line. The interrupt flag lines from all Modular System Units are, similarly, logically "OR" ed to provide the serial I/O interrupt flag to the microprocessor.

This flag may be used to generate a master interrupt within the microprocessor.

#### 3.1 Interrupt Structure

Eight decision flag bits are provided to designate a particular interrupt condition. When any of these bits are high, the master interrupt flag goes high. The master interrupt flag bit may be tested by the microprogram to detect the interrupt condition. When the microprocessor has recognized the interrupt request, it may respond accordingly.

The normal procedure for acknowledging an interrupt is to regularly monitor the master interrupt flag. This can be done by executing a decision instruction on the interrupt flag whenever returning from a subroutine. One must assume, of course, that the maximum allowable interrupt response time is not exceeded by the maximum subroutine execution time.

Normally, the interrupt flag is low and only 2 machine cycle times (480 n seconds) are wasted looking at the flag. If, however, the flag is high, the microprocessor can proceed to execute an interrupt servicing routine which checks the 8 interrupt flags in order of their priority.

The master interrupt flag may be disabled or enabled by using the appropriate instructions.

Once the flag responsible for generating the interrupt is found, it may be serviced. The interrupting flag should, however, be cleared prior to servicing the interrupt so that higher level interrupts may be monitored while servicing the lower level one.

Decision flags may be assigned to be interrupt status flags by strapping them into the master interrupt circuit. Flags normally assigned as interrupts are:

> Push Down Stack Flag Console Alarm Interrupt Power Fail Interrupt Relinquish Bus Flag Parallel I/O Interrupt Flag Serial I/O Interrupt Flag Real Time Clock Flag

#### 3.2 Parallel I/O

As explained in section  $1.1\emptyset$ , the data memory and parallel I/O peripherals share the same high-speed bus. Thus the microprocessor views parallel I/O peripheral devices as active memory locations which perform special functions. There are some differences, however, between the way the data memory and the parallel I/O devices are operated upon by the microprocessor. It may be seen in Fig. 2.2, there are 3 control and 2 flag lines on the parallel I/O bus that are not used for accessing data memory. These are:

- a) <u>POP</u>: Power on pulse generated during a PORC condition. It is used for resetting all I/O devices.

- b) PFL: I/O status flag usually indicates that I/O device being addressed is ready.

- c) <u>PIN:</u> I/O interrupt flag used to indicate that at least one I/O device is interrupting.

- d) IAK: Interrupt acknowledge signal used for clearing the interrupt flag of the I/O device being addressed.

- e) <u>RBC</u>: This line does not go onto the I/O bus, but rather, is used to disable the microprocessor from both the serial and parallel I/O busses.

In some cases the parallel I/O status flag may be used to delay the master clock until the device is ready, as explained in section 1.9.

#### 3.3 Multiprocessor Configuration

A capability exists whereby the AES microprocessor can disable itself from both the serial and parallel I/O busses. When a relinquish bus flag is sensed during an interrupt acknowledge routine, it is possible to disable all I/O line drivers and receivers from the I/O busses by executing a relinquish bus control instruction. This command is useful when there are 2 microprocessors on the same bus and where one of them is waiting on standby to take over bus control in the case of microprocessor failure.

3.4 I/O Instructions

The I/O instruction group is used for all communication between the computer and the peripheral devices that supply and receive data.

The RAM address instructions and the M=D and D=M instructions are also used for selecting, Read/Write control and read enabling of parallel I/O devices. As these have already been explained in sections 2.2, 2.6 and 2.7, they will be omitted from the following description.

|       | •       |        |        |

|-------|---------|--------|--------|

| U-Reg | gister. | Instru | ctions |

3.4.1

| Mnemonicm | ASCII | Description                                                                                                   |

|-----------|-------|---------------------------------------------------------------------------------------------------------------|

| U=Ø       | FG    | Clear the U-Register (serial<br>I/O register).                                                                |

| U=U#D     | FD    | Form the logical "OR" function<br>of the D bus and U-register<br>words and store this into the<br>U-register. |

#### 3.4.2 I/O Register Select Instruction

| Mnemonic                                                     | ASCII                                         | Description                                                                                                                                                                     |

|--------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RG=Ø<br>RG=1<br>RG=2<br>RG=3<br>RG=4<br>RG=5<br>RG=6<br>RG=7 | FX<br>FY<br>FZ<br>F[<br>F∖<br>F]<br>F∫<br>F ← | Set the least significant 3<br>bits of the serial I/O select<br>address to the octal number n<br>where $n = \emptyset$ to 7. This<br>defines the serial I/O register<br>number. |

| RG=B                                                         | FM                                            | Set the least significant 3<br>bits at the serial I/O select<br>address equal to the least<br>significant 3 bits of the B-<br>register output.                                  |

These instructions form a mutually exclusive function set.

#### 3.4.3. I/O Channel Select Instruction

The following instructions set the most significant 5 bits of the serial I/O select address to the number N, where N -  $\emptyset$  to 31. This defines the serial I/O channel number.

| Mnemonic | ASCII | Mnemonic           | ASCII         |

|----------|-------|--------------------|---------------|

| CHL=Ø    | G@    | CHL=16             | GP            |

| CHL=1    | GA    | CHL=17             | GQ            |

| CHL=2    | GB    | CHL=18             | GR            |

| CHL=3    | GC    | CHL=19             | GS            |

| CHL=4    | GD    | $CHL = 2\emptyset$ | $\mathbf{GT}$ |

| CHL=5    | GE    | CHL=21             | GU            |

| CHL=6    | GF    | CHL=22             | GV            |

| CHL=7    | GG    | CHL=23             | GW            |

| CHL=8    | GH    | CHL=24             | GX            |

| CHL=9    | GI    | CHL=25             | GY            |

| CHL=1Ø   | GJ    | CHL=26             | GZ            |

| CHL=11   | GK    | CHL=27             | GE            |

| CHL=12   | GL    | CHL=28             | G١            |

| CHL=13   | GM    | CHL=29             | GJ            |

| CHL=14   | GN    | $CHL=3\emptyset$   | GŤ            |

| CHL=15   | GO    | CHL=31             | G←            |

#### 3.4.4 Serial I/O CLOCK, LOAD and R/W Instructions

| Mnemonic | ASCII | Description                                |

|----------|-------|--------------------------------------------|

| CLK=Ø    | DU    | Clear the I/O clock line                   |

| CLK=1    | FU    | Set the I/O clock line                     |

| LD=Ø     | DV    | Clear the I/O load line                    |

| LD=1     | FV    | Set the I/O load line                      |

| R/W=R    | DW    | Set the I/O R/W line to $\emptyset$ (read) |

| R/W=W    | FW    | Set the I/O R/W line to 1 (write)          |

These instructions are all latching functions.

#### 3.4.5 Relinquish Bus Control Instructions

| Mnemonic | ASCII | Description                                                                                                                         |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| RBC      | FP    | Disable all serial and<br>parallel I/O line drivers<br>and receivers                                                                |

| EBC      | DP    | Enable all serial and<br>parallel I/O line drivers<br>and receivers. These are<br>automatically enabled during<br>a PORC condition. |

| JIS,RBF  | ВР    | Jump if relinquish bus flag<br>is set.                                                                                              |

| JIC,RBF  | @P    | Jump if relinquish bus flag is clear.                                                                                               |

3.4.6 Serial I/O Timing Instructions

| Mnemonic | ASCII | Description                                                                                                                |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------|

| SIO      | FO    | Start the automatic transfer<br>of serial data between the<br>U-register and the addressed<br>serial I/O device. Data will |

|          |       | be transferred into or out of<br>the U-register depending on the<br>status of the R/W line.                                |

This is a strobe function.

29.

| Mnemonic | ASCII |

|----------|-------|

| JIS, IOR | BB    |

| JIC, IOR | @B    |

#### Description

Description