**ADVANCED DIGITAL**

# MULTI SLAVE Product Reference Manual

PRELIMINARY COPY

USA OFFICE 5432 PRODUCTION DRIVE HUNTINGTON BEACH, CA 92649 TELEPHONE : (714) 891-4004 TELEX: 183210 ADVANCED HTBH UNITED KINGDOM OFFICE 27 PRINCESS STREET HANOVER SQUARE, LONDON W1R8NQ UNITED KINGDOM 409-0077 / 409-3351 TLX 265840 FINEST

### MULTI SLAVE PRODUCT REFERENCE MANUAL

Revision A.0

Advanced Digital Corporation 5432 Production Drive Huntington Beach, California 92649 USA Telephone: (714) 891-4004 Telex: 183210 ADVANCED HTBH Advanced Digital (U.K.) Ltd. 27 Princess Street Hanover Square London, U.K. (01) 409-0077 Copyright (C) 1985 by Advanced Digital Corporation 5432 Production Drive Huntington Beach, California 92649

All rights reserved. No part of this publication may be reproduced, transmitted, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of Advanced Digital Corporation.

NOTICES

Page i

#### CONTENTS

| NOTICES<br>TABLE OF CONTENTS                                                                                                                                                                                                                                                             | 1<br>1 1                               |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|

| SECTION I                                                                                                                                                                                                                                                                                | 1-1                                    |  |  |  |  |  |  |

| Introduction.<br>Unpacking/Packing Instructions.<br>Installation.<br>Warranty and Return Procedure.<br>Features and Options.<br>Functional Flow.<br>Multi Slave Product Specification.<br>Factory Configuration.<br>General Notes.                                                       | 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6 |  |  |  |  |  |  |

| SECTION II                                                                                                                                                                                                                                                                               | 2-1                                    |  |  |  |  |  |  |

| Power On/Reaet Eventa.2-5PROM Selection Jumpera.2-6Interrupt Selection Jumpera.2-6Slave Base Address Selection.2-7Slave Status Port Definitions.2-8Master/Slave Communications.2-9I/O Address Map.2-10Bank and PROM Select Port.2-11Serial I/O Controller.2-12Counter/Timer Circuit.2-13 |                                        |  |  |  |  |  |  |

| SECTION III                                                                                                                                                                                                                                                                              | 3-1                                    |  |  |  |  |  |  |

| Fault Isolation and Troubleshooting<br>SECTION IV<br>Multi Slaye Monitor                                                                                                                                                                                                                 | 4-1                                    |  |  |  |  |  |  |

| APPENDIX A - S-100 Bus Pinout<br>APPENDIX B - Multi Slave Jumper Options<br>APPENDIX C - I/O Connector Pinouts<br>APPENDIX D - I/O Port Assignments<br>APPENDIX E - Multi Slave Schematic<br>APPENDIX F - Multi Slave Parts List<br>APPENDIX G - PS/NET Serial Interface Adaptor         | A-1<br>B-1<br>C-1<br>D-1<br>E-1<br>F-1 |  |  |  |  |  |  |

| APPENDIX H - Signetics 2681 DUART Data Sheet                                                                                                                                                                                                                                             |                                        |  |  |  |  |  |  |

1

| Illustration                                                                     | a:                                                                                                                             |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-1<br>Figure 1-2                                                         | Multi Slave Block Diagram                                                                                                      |

| Figure 2-1<br>Figure 2-2<br>Figure 2-3<br>Figure 2-4<br>Figure 2-5<br>Figure 2-6 | PROM Selection Jumpers                                                                                                         |

| Tables:                                                                          |                                                                                                                                |

| Table 2–1<br>Table 2–2<br>Table 2–3<br>Table 2–4                                 | Master S-100 Port Assignments2-3<br>I/O Port Assignments2-6<br>Bank Select Bit Definitions2-7<br>Serial I/O Cable Connector2-8 |

.

## SECTION I

#### INTRODUCTION

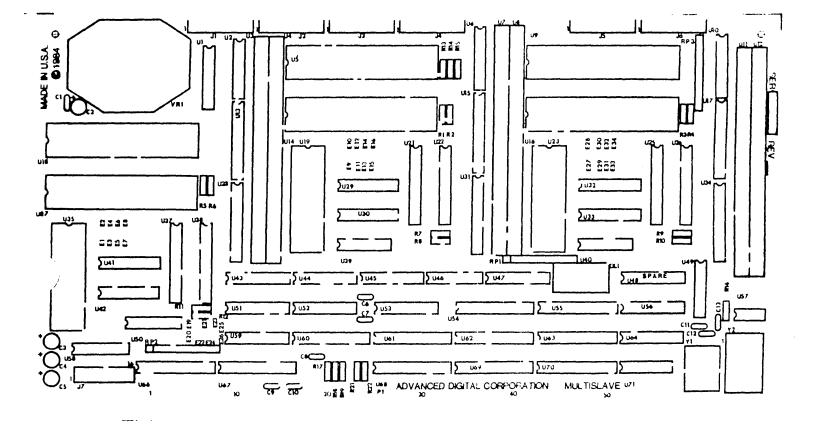

This Product Reference Manual provides information to install, utilize and maintain the Advanced Digital Corp.'s Multi Slave S-100 bus compatible computer. The Multi Slave is a single printed circuit board, conforming to the IEEE-696 form factor of 5.25 inches by 10 inches (13.33 cm by 25.4 cm), providing three independent 8 MHz 280 central processors, each with two 64k byte banks of memory, two serial I/O ports, and a counter/timer.

#### UNPACKING/PACKING INSTRUCTIONS

When the Multi Slave is delivered by a transfer company, it must be carefully inspected for damage. Prior to accepting delivery, carefully inspect the shipping container for obvious damage. If damage is evident, note it on the waybill and require that the delivery agent sign the waybill. Notify the transfer company immediately, and submit a damage report to the carrier.

Remove the Multi Slave and any accessory items from the shipping container. Retain the shipping container any packing material for possible reshipment. Leave the Multi Slave in its antistatic envelope until installation time.

#### INSTALLATION

After verifying that the intended enclosure for the Multi Slave will provide adequate power and air flow, remove the Multi Slave from its anti-static envelope. Inspect and verify that the configuration jumpers on the Multi Slave are correct for the Multi Slave's intended utilization. Attach I/O cables to the connectors provided for serial I/O as required. Insert the Multi Slave printed circuit board into a suitable S-100 bus slot connector.

#### WARRANTY AND WARRANTY RETURN PROCEDURE

Advanced Digital Corporation warrants that its products will be free from defects in material and workmanship for a period of 360 days of shipment from the factory.

If a customer experiences a defect in either workmanship or materials during the warranty period, notify your supplier immediately. Your supplier may repair the Multi Slave or determine if some other action is to be taken. In the event that a return of the Multi Slave is deemed neccessary, obtain a RETURN MATERIAL AUTHORIZATION (RMA) NUMBER from your supplier.

Repack the Multi Slave and any accessory items in the original packing material and ship it in accordance with your supplier's shipping instructions. Make sure the RMA number is clearly marked on the shipping label. Your supplier will not accept delivery of a return shipment without the proper RMA number.

The Multi Slave as delivered does not generate, use, or radiate radio frequency energy. However, after installation and application of power, the Multi Slave may generate, use, or radiate radio frequency energy. Advanced Digital Corporation recommends that the Multi Slave be installed in an enclosure which complies with the provisions for computing devices pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference.

#### FEATURES AND OPTIONS

The Multi Slave provides the following features:

- o Three independent 8-bit, 8 MHz 280 Microprocessors

- Each CPU has 128k of memory, configured as two 64k

byte banks, with a 1k to 16k area of common (shared)

memory.

- o Two asynchronous serial I/O ports per CPU. Level conversion to EIA RS-232C or RS-422 standards is provided via the PS/NET (paddle card) accessory.

- o Independent baud rate selection on each serial port

- o Counter/Timer providing real time clock capability

- User selectable PROM, jumper configurable for one of the following: 2716, 2732, 2764, 27128, or 27256.

- o IEEE-696 S-100 Bus Compatibility

- Automatic power-on/reset bootstrap loader and resident monitor/debugger utility.

#### FUNCTIONAL FLOW

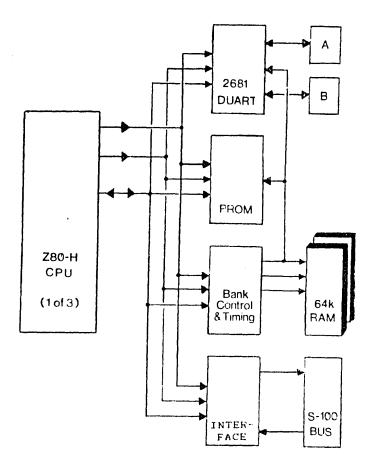

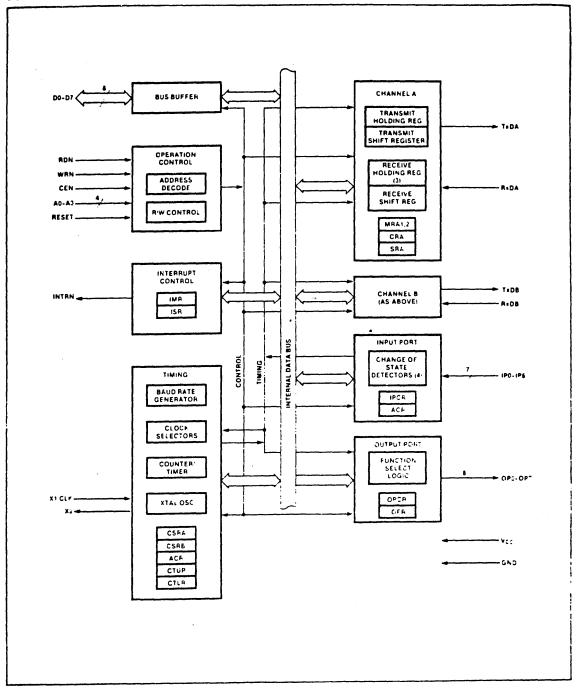

Figure 1-1 illustrates the major functional components of the Multi Slave computer board. Initially, immediately following the power-on/reset event, all three processors are held in a reset state. Each processor must be individually activated by a network master. Once the master has activated a Multi Slave processor, the selected slave CPU then begins executing the instructions provided by the onboard EPROM. Depending upon user response and intervention, the processor will either initiate the execution of the resident Monitor/Debug program, or begin the download request sequence to receive an operating system.

## MULTI SLAVE PRODUCT SPECIFICATION

Physical and Environmental:

| Form Factor                         | IEEE-696 S-100 standard                                                                                                            |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Size                                | 5.25 inches x 10.0 inches x .75 inches                                                                                             |

| Weight                              | 14 oz.                                                                                                                             |

| Temperature<br>operating<br>storage | 0 to 50 degrees Celcius<br>-65 to 150 degrees Celcius                                                                              |

| Humidity                            | 0 to 95%, non-condensing                                                                                                           |

| Altitude                            | 0 to 10,000 feet (operating)                                                                                                       |

| Power Requrementa:                  |                                                                                                                                    |

|                                     | +5VDC @ xx.x Amps (xx Watts)                                                                                                       |

| Power Regulation                    | On board, providing 4.75 to 5.25VDC                                                                                                |

| Cooling                             | 1-5 CFM (cubic feet per minute) air flow                                                                                           |

| Power Supply Requiremen             | ts:                                                                                                                                |

| Unregulated                         | + 7VDC Minimum<br>+11VDC Average<br>+25VDC Maximum (peak)                                                                          |

|                                     | +14.5VDC Minimum<br>+21.5VDC Average<br>+35.0VDC Maximum (peak)<br>-14.5VDC Minimum<br>-21.5VDC Average<br>-35.0VDC Maximum (peak) |

| Functional Specificatio             | n:                                                                                                                                 |

| Processor                           | Zilog Z80H                                                                                                                         |

| Memory                              | 128k Dynamic RAM                                                                                                                   |

| Processor Clock                     | 8.000 MHz                                                                                                                          |

Serial Controller

Signetics 2681 DUART

FACTORY CONFIGURATION

The factory standard configuration of the Multi Slave uses a 2764 EPROM, and does not utilize the S-100 Vectored Interrupt Lines. The base address of the board is jumpered for I/O address 90H at jumper block E-19 thru E-26 (lower left quadrant).

#### GENERAL NOTES

The Multi Slave contains three independent Zilog Z80-H CPUs. The principal I/O device for each processor is the Signetics 2681 DUART (Dual Universal Asynchronous Receiver/Transmitter). This particular device was chosen for its many features, which include an internal dual baud rate generator and counter/timer.

Several types of PROMs are supported by the Multi Slave, based on jumper options. The PROM types supported are as follows: 2716, 2732, 2764, 27128 and 27256. PROM addressing begins at 0000H.

Each processor contains a total of 128k of user available memory, configured as two 64k banks, and is selectable through software.

There is only one interrupt source on the Multi Slave, which is provided by the DUART. Typically, the Z80 CPU will be operated using Mode 1 interrupts (see the Zilog Z80 Technical Manual for a discussion of Z80 interrupt modes).

Each alave is also capable of interrupting the master via the S-100 vectored interrupt lines. This will be discussed in detail later.

Each 280 CPU is driven by a central 8 MHz oscillator; the three DUARTs are driven by a common 3.6864 MHz crystal.

# SECTION II

#### POWER-ON/RESET EVENTS

Each Multi Slave CPU is held in a reset state until such time as the master enables the operation of a slave. The master enables a slave by issuing an output byte to the slave's base address with bit D4 reset. The PROM is automatically selected, and instruction execution begins at address 0000H.

The ADC supplied PROM initializes both channels of the DUART to 9600 baud, then tests channel A for an available input character. If a character is available, the Multi Slave monitor is activated which issues the following message to the terminal on channel A:

Multi Slave Monitor Version 1.x Generated MM-DD-YY Copyright (C) 1985 Advanced Digital Corporation

Enter '?' for HELP

\*

A complete discussion of the Multi Slave monitor may be found in section IV of this manual.

If an input character is not available at serial channel A within approximately 100 milliseconds, the startup program will enter the cold boot process, sending an operating system download request to the master processor over the S-100 bus.

#### PROM SELECTION JUMPERS

Each CPU has a jumper block to select the PROM type. Use the following table to set these jumpers.  $F_{1}-6 = EA-16 = E27-3^{4}$

| 1 0 0 2        | PROM TYPE   | JUMPER        |

|----------------|-------------|---------------|

| 3004           |             |               |

| 5006           | 2716 (2K)   | 3-5, 4-6      |

| 7008           | 2732 (4K)   | 5-7, 4-6      |

| · ·            | 2764 (8K)   | 1-3, 5-7      |

| TYPICAL JUMPER | 27128 (16K) | 1-3, 6-8, 5-7 |

| BLOCK          | 27256 (32K) | 1-2, 6-8, 5-7 |

Figure 2-1 Hulti Slave PROM Selection Jumpers

#### INTERRUPT SELECTION JUMPERS

Each Multi Slave CPU may interrupt the master processor on one of two S-100 vectored interrupt lines. Selection of interrupts is as follows:

| MULTI SLAV      | E JUMPER BLOCK | S-100 BUS        |

|-----------------|----------------|------------------|

|                 | <br>7 لا       |                  |

| Multi Slave CPU | 0 10 02        | INTO* (pin 4)    |

| •• •• ••        | " 30 04        | INT1* (pin 5)    |

| Multi Slave CPU | 1 50 06        | 5 INT2* (pin 6)  |

| ** ** **        | • 7 0 0 6      | 3 INT3* (pin 7)  |

| Multi Slave CPU | 2 90 01        | O INT4* (pin 8)  |

|                 | • 11 0 0 1     | 2 INT5* (pin 9)  |

| No Connection   | n 13001        | 4 INT6* (pin 10) |

| ** **           | 15 0 0 1       | 6 INT7* (pin 11) |

#### Figure 2-2 Multi Slave Interrupt Jumper Selection

If the interrupt selection structure shown above is not suitable, wire wrap connections between the jumper block pins may be used in place of jumper plugs, thus allowing any given Multi Slave CPU to use any of the eight S-100 vectored interrupt lines.

#### SLAVE BASE ADDRESS SELECTION

Each Multi Slave CPU occupies four of the master's I/O ports, though only three are actually used by each CPU. Base address selection of the Multi Slave board is as follows: E/Q - E2b

(7)(6)(5)(4)

|     | 1 | З | 5 | 7 |     |                                       |

|-----|---|---|---|---|-----|---------------------------------------|

|     | 1 | 1 | 1 | 1 |     |                                       |

|     | 0 | 0 | 0 | 0 |     |                                       |

| MSB |   |   |   |   | LSB | Address selection uses LOW TRUE LOGIC |

|     | 0 | 0 | 0 | 0 |     | (no jumper=1, jumpered=0) and repre-  |

|     | 1 | 1 | ł | 1 |     | sents the four most significant bits  |

|     | 2 | 4 | 6 | 8 |     | of the base address.                  |

#### Figure 2-3 Multi Slave Base Address Selection

Example:

| BASE ADDRESS | JUMPERS       |

|--------------|---------------|

|              |               |

| 70H          | 1 - 2         |

| 80H          | 3-4, 5-6, 7-8 |

| HOE          | 3.4, 5-6      |

| AOH          | 3-4, 7-8      |

| вон          | 3-4           |

| Сон          | 5-6, 7-8      |

| DOH          | 5-6           |

|              |               |

If, for example, the base address was 80H, the three CPUs would be addressed as follows:

| CPU | #0 | 80H | ; | uses | 80Н, | 81H, | and | $\sim 5 \mathrm{R}$ | (83H | not  | used) |

|-----|----|-----|---|------|------|------|-----|---------------------|------|------|-------|

| CPU | #1 | 84H | ; | uses | 84H, | 85H, | and | 36H                 | (87H | пot  | used) |

| CPU | #2 | 88H | ; | uses | 88H, | 89H, | and | HAB                 | (8BH | not. | used) |

The master (S-100) data port assignments are as follows:

| BASE ADDRESS | TYPE | FUNCTION                                                          |

|--------------|------|-------------------------------------------------------------------|

|              |      |                                                                   |

| +0           | R/W  | Read Slave Status (see details below)<br>Write Control bits       |

| +1           | R/W  | S-100 Data Port                                                   |

| +2           | R/W  | Read = De-assert ALIVE* bit<br>Write= De-assert SLAVE MESSAGE bit |

#### Table 2-1 Master S-100 Port Assignments

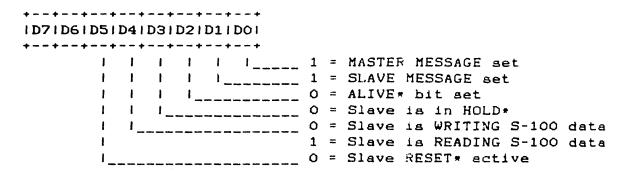

SLAVE STATUS PORT (read by Master Processor)

STATUS PORT (written by Master Processor)

+--+--+ ID7ID6ID5ID4ID3ID2ID1ID0I +--+--+ I I I = set MASTER MESSAGE bit I = reset slave processor

#### Figure 2-4 Master Status Port Bit Definitons

Note that bits D6 and D7 of the STATUS PORT are not used, and are on (1) when the port is read by the Master Processor. Note also that there are four low active terms; ALIVE\*, HOLD\*, WRITE\*, and RESET\*.

#### HASTER/SLAVE COMMUNICATIONS

For the master processor to send data to the slave, the slave must be reading the S-100 data port. Conversiy, for the slave to send data to the master, the slave must write to the S-100 data port before the master reads it. As mentioned earlier, when the slave is reading or writing to the S-100 data port, it is placed in a HOLD (wait) condition, and released to resume processing when the Master Processor writes or reads the corresponding port. This ensures that the master and slave(s) remain in synchronization during bus communication; reliable network operation is achieved when the other status bits (ALIVE\*, READ/WRITE\*, and HOLD\*) are implemented as part of a communications protocol.

The Master Processor may reset a alave processor at any time by issuing an output to the appropriate slave status port with bit D4 set. To reactivate the slave, the master must again issue an output byte to the slave's status port with bit D4 reset, followed by a short post-reset delay. An example of this sequence is shown below:

| SL_RES: | LD   | A,10H       | ; | SET BIT D4                   |

|---------|------|-------------|---|------------------------------|

|         | OUT  | (SLVBASE),A | ; | OUTPUT TO SLAVE BASE ADDRESS |

|         | LD   | B,16        | ; | LEAVE THE BIT SET            |

| SL_R05: | DJNZ | SL_R05      | ; | FOR A SHORT TIME             |

|         | XOR  | NOT 10H     | ; | TURN OFF BIT D4              |

|         | OUT  | (SLVBASE),A | ; | UN-RESET THE SLAVE           |

|         | LD   | B,16        | ; | SET UP FOR POST-RESET DELAY  |

| SL_R10: | EX   | (SP),HL     | ; | THIS IS A                    |

|         | ΕX   | (SP),HL     | ; | VERY EFFECTIVE               |

|         | DJNZ | SL_R10      | ; | TIME WASTER                  |

|         | RET  |             | ; | RETURN TO CALLER             |

The suggested handshake mechanism between the master and slave is as follows (for transmission from slave to master): the slave first asserts the SLAVE MESSAGE bit. The master may see this by polling (reading the slave status port), or the Multi Slave may be configured to cause an interrupt on the master. In either case, once the SLAVE MESSAGE bit has been asserted, the slave CPU then outputs its first data byte to the S-100 bus communications port. Upon doing so, the slave CPU is forced into a wait condition, which the master must verify by testing the WRITE\* and HOLD\* bits at the slave status port. Once the master has determined that both signals are true, it may then read the byte waiting at the S-100 data port. The slave is released to resume processing, free to continue sending subsequent data bytes, etc.

In a master to slave transmission, the master must assert the MASTER bit, which the slave sees by polling its' status port. Upon detecting the active MASTER bit, the slave must reset it (indicating to the master that the slave is ready to accept the measage), and immediately issue a read to the S-100 data port. Again, the slave processor is forced into a wait condition. which the master must verify by testing the READ and HOLD\* bits at the slave status port. Once the master has determined that both signals are active, it may then write the data byte to the S-100 data port. The slave is released to resume processing, free to continue receiving subsequent data bytes, etc.

The following page provides a brief example of this master/slave dialogue:

MASTER PROCESSOR (RECEIVING MESSAGE FROM SLAVE)

| IN     | A, (SLVSTAT) | ; GET SLAVE STATUS                    |

|--------|--------------|---------------------------------------|

| BIT    | SLVMSG,A     | ; IS SLAVE MESSAGE BIT SET?           |

| RET    | NZ           | ; NO, RESUME OTHER TASKS (ACTIVE LOW) |

| OUT    | (MSGRST),A   | ; OUTPUT CLEARS SLAVE MESSAGE BIT     |

|        |              | ; (CONTENTS OF A-REG INSIGNIFICANT)   |

| WAIT1: |              |                                       |

| IN     | A,(SLVSTAT)  | ; GET SLAVE STATUS BITS               |

| BIT    | SLVWRT,A     | ; IS SLAVE WRITING TO S-100 PORT?     |

| JR     | NZ,WAIT1     | ; LOOP IF NOT                         |

| BIT    | SLVHLD,A     | ; IS SLAVE IN A HOLD CONDITION?       |

| JR     | NZ,WAIT1     | ; LOOP IF NOT                         |

| IN     | A, (SLVDATA) | ; ALL IS READY - GET THE DATA BYTE    |

| RET    |              | ; AND RETURN TO CALLING TASK          |

MASTER PROCESSOR (SENDING MESSAGE TO SLAVE)

|       | LD  | A,0000010B   | ; | SET MASTER MESSAGE BIT           |

|-------|-----|--------------|---|----------------------------------|

|       | OUT | (SLVSTAT),A  | ; | SO THE SLAVE WILL SEE IT         |

| WAIT2 | 2:  |              |   |                                  |

|       | IN  | A,(SLVSTAT)  | ; | GET SLAVE STATUS                 |

|       | BIT | MASTER,A     | ; | HAS THE SLAVE RESET IT YET?      |

|       | JR  | NZ,WAIT2     | ; | LOOP UNTIL HE HAS DONE SO        |

| WAITS | 3:  |              |   |                                  |

|       | IN  | A, (SLVSTAT) | ; | GET SLAVE STATUS AGAIN           |

|       | BIT | SLVWRT,A     | ; | IS SLAVE READING THE S-100 PORT? |

|       | JR  | Z,WAIT3      | ; | LOOP IF NOT                      |

|       | BIT | SLVHLD,A     | ; | IS SLAVE IN A HOLD CONDITION?    |

|       | JR  | NZ,WAIT3     | ; | LOOP IF NOT                      |

|       | LD  | A,(HL)       | ; | GET BYTE TO SEND                 |

|       | OUT | (SLVDATA),A  | ; | SEND IT TO THE SLAVE             |

|       | RET |              | ; | AND RETURN TO CALLING TASK       |

|       |     |              |   |                                  |

SLAVE PROCESSOR (RECEIVING MESSAGE FROM MASTER)

| IN  | A, (MASTER)   | ; | CLEAR MASTER MESSAGE BIT         |     |

|-----|---------------|---|----------------------------------|-----|

| IN  | A, (DATAPORT) | ; | AND IMMEDIATELY READ THE S-100 P | ORT |

| RET |               | ; | RETURN TO CALLING TASK           |     |

SLAVE PROCESSOR (SENDING MESSAGE TO MASTER)

| IN  | A,(SLVMSG)   | ; SET SLAVE MESSAGE BIT               |

|-----|--------------|---------------------------------------|

| LD  | А,В          | ; B-REG HAS DATA BYTE TO SEND         |

| OUT | (DATAPORT),A | ; OUTPUT DATA BYTE TO S-100 DATA PORT |

| RET |              | ; RETURN TO CALLING TASK              |

Note that these examples transmit and receive only a single byte at a time and provide only a skeletal communications protocol. The slave may utilize the 280 block input and output instructions to receive and transmit any number of bytes to the master, though the user should employ a slightly more sophisticated protocol when doing so. In typical networking environments, the first byte transmitted contains the length of the message to follow. Implementation of such networking schemes is left to the user.

#### BOOTSTRAP SOFTWARE

The following program will provide the user with a bootstrap facility which follows the protocol set forth in the prior section. This program is identical to that contained in the Multi Slave monitor PROM, and assumes that an intermediate loader will be received from the master.

| SLVMSG<br>SALIVE<br>SDATA<br>SHMEM | EQU 20H<br>EQU 60H<br>EQU 0070H<br>EQU 8000H | ; I/O READ SETS SLAVE MESSAGE BIT<br>; I/O READ SETS SLAVE ALIVE BIT<br>; B=MESSAGE LENGTH, C=PORT ADDRESS<br>; ONLY ADDRESSES ABOVE 8000H ARE<br>; ACCESSABLE WHILE PROM IS ENABLED |

|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT:                              |                                              |                                                                                                                                                                                      |

| IN                                 | A,(SLVMSG)                                   | ; SET SLAVE MESSAGE BIT                                                                                                                                                              |

| IN                                 | A,(SALIVE)                                   | ; SET SLAVE ALIVE BIT                                                                                                                                                                |

| LD                                 | BC,SDATA                                     | ; B=BYTE COUNT (O=256 BYTES)                                                                                                                                                         |

|                                    |                                              | ; C=PORT ADDRESS                                                                                                                                                                     |

| OUT                                | (C),B                                        | ; SEND BYTE COUNT FIRST                                                                                                                                                              |

| LD                                 | HL, SHMEM                                    | ; ADDRESS TO STORE INCOMING MESSAGE                                                                                                                                                  |

|                                    |                                              | ; (WHICH WILL BE THE INTERMEDIATE                                                                                                                                                    |

|                                    |                                              | ; LOADER PROGRAM)                                                                                                                                                                    |

| INIR                               |                                              | ; RECEIVE ENTIRE MESSAGE FROM MASTER                                                                                                                                                 |

| JP                                 | SHMEM                                        | ; BRANCH & EXECUTE INTERMEDIATE LOADER                                                                                                                                               |

#### **I/O ADDRESS MAP**

Each Multi Slave CPU has an identical I/O address map. The port assignments are as follows:

| ADDRESS (Hex) | TYPE | FUNCTION                                                             |

|---------------|------|----------------------------------------------------------------------|

|               |      |                                                                      |

| 00-0F         | R/W  | DUART Data/Control (see Signetics<br>2681 Documentation for details) |

| 10-1F         |      | Not Used                                                             |

| 20-2F         | R    | Asserts SLAVE MESSAGE bit                                            |

| 30-3F         | R    | De-asserts MASTER MESSAGE bit                                        |

| 40-4F         | ω    | BANK/PROM SELECT (details follow)                                    |

| 50-5F         | R    | STATUS PORT (MASTER and SLAVE bits)                                  |

| 60-6F         | R    | Asserts SLAVE ALIVE* bit                                             |

| 70-7F         | R/W  | S-100 DATA PORT                                                      |

Table 2-2 I/O Port Assignments

The user should be aware that although it would appear that the S-100 data ports would collide with one another, they are actually physically separated in the hardware. This is explained a bit more clearly by the following diagram:

| SLAVE PROCESSOR NU | MBER MAS | STER PROCESSOR   |

|--------------------|----------|------------------|

|                    | 7онІ/с   |                  |

| #1 I/O ADDRESS     | 70HI/C   | BASE ADDRESS + 4 |

| #2 I/O ADDRESS     | 70HI/C   | BASE ADDRESS + 8 |

#### Figure 2-5 Slave Status Port Bit Definitions

#### BANK AND PROM SELECT PORT

The BANK/PROM SELECT port specifies which of the two 64k memory banks is to be active, and whether or not the PROM is to be selected. The bit definitions for this port are as follows:

#### Figure 2-6 Bank and Prom Select Port Bit Definitions

| Bits D4-D7<br>Hex Value | Shared<br>Amount |

|-------------------------|------------------|

|                         |                  |

| 0                       | 16k              |

| 1                       | 15k              |

| 2                       | 14k              |

| З                       | 13k              |

| 4                       | 12k              |

| 5                       | 11k              |

| 6                       | 10k              |

| 7                       | 9k               |

| 8                       | 81               |

| 9                       | 7 k              |

| А                       | 6k               |

| В                       | 5k               |

| С                       | 4k               |

| D                       | Зk               |

| E                       | 2k               |

| F                       | 1 k              |

#### Table 2-3 Bank Select Bit Definitions

NOTE: Bank O and 1 are mutually exclusive and must not be set active at the same time. When the PROM is selected, only memory locations 8000H through OFFFFH may be accessed for RAM read and write operations.

#### SERIAL 1/O CONTROLLER

The Multi Slave provides two independent serial I/O channels per CPU, both contained in one aerial I/O controller, the Signetica 2681 Dual Asynchronous Receiver/Transmitter (DUART). The DUART contains two internal, independent baud rate generators, capable of producing 18 user selectable baud rates. Level conversion to EIA RS-232 or RS-422 level is provided by an external circuit assembly called the PS-NET.

#### SERIAL CHANNEL CONNECTORS

Connectors for each serial I/O channel are located across the top of the Multi Slave board (see figure 1-1 for exact placement). Each connector has the following pinout:

| PIN NO. | SIGNAL NAME             | DIRECTION      |

|---------|-------------------------|----------------|

|         |                         |                |

| 1       | DCD Data Carrier Detect | input          |

| 2       | DSR Data Set Ready      | input          |

| * 3     | *** see note below      | input/output   |

| 4       | RXD Receive Data        | input          |

| 5       | CTS Clear to Send       | input          |

| 6       | TXD Transmit Data       | output         |

| 7       | RTS Request to Send     | output         |

| 8       | DTR Data Terminal Ready | output         |

| 9       | CLK Tx/Rx Clock         | input/output   |

| 10      | GND Signal Ground       | ground         |

| 11      | N/C                     |                |

| 12      | +16 VDC                 | supply voltage |

| 13      | -16 VDC                 | supply voltage |

| 14      | +5 VDC                  | supply voltage |

\* On channel A, this term is RNG (ring detect) and may be connected to the ring detect line on a modem. This line has no connected on channel B.

Table 2-4 Serial I/O Cable Connector

#### COUNTER/TIMER CIRCUIT

The counter/timer circuit is contained on the DUART device. As its name implies, it may be used as a timer (programmable divider) or a counter, providing an appropriate indication when the specified countdown value has reached zero.

It should be noted that unlike the Z80 CTC, the DUART's counter/timer uses a 16-bit countdown register, providing much greater flexibility in its application.

Appendix H contains the data sheet for the Signetics 2681 device.

SECTION III

#### FAULT ISOLATION

Fault isolation is the process of identifying a fault and the resultant cause of the fault to the lowest possible level. This section deals with hardware fault isolation and is generally independent of software considerations.

Prior to any attempt at fault isolation, a test environment must be validated. Generally, the test environment will consist of an S-100 chassis, motherboard, power supply, S-100 extender card, and a known good Multi Slave. Validation consists of removing all other S-100 circuit cards from the chassis, and any other devices loading the +8, +16, and/or -16 VDC power supplies.

Having removed all circuit boards from the motherboard, verify that the following voltages referenced to ground (S-100 bus pin 50 and 100) are within the tolerances listed below:

| S-100 PIN | DEFINITION | MINIMUM | AVERAGE | MAXIMUM |

|-----------|------------|---------|---------|---------|

|           |            |         |         |         |

| 1         | + 8 VDC    | +7.0    | +11.0   | +25.0   |

| 51        | + 8 VDC    | +7.0    | +11.0   | +25.0   |

| 2         | +16 VDC    | +14.5   | +21.5   | +35.0   |

| 52        | -16 VDC    | -35.0   | -21.5   | -14.5   |

The above conditions must be met before proceeding with the next test.

Step 1: Visual Verification

Inspect the suspect Multi Slave to verify that components are correctly installed and properly seated in their sockets. Components may be compared against a known good Multi Slave. All DIP components have the same pin 1 orientation.

Step 2: On Board +5 VDC Regulation

Remove power from the motherboard. Insert the S-100 extender card into a suitable slot in the motherboard, then insert the Multi Slave into the extender card socket. Apply power and measure the voltage at U1-16. This voltage must be between 4.75 and 5.25 VDC.

Step 3: Clock Verification

Verify the clock frequencies at the following locations:

| U57-7 | 80ns  | central clock distributed to all CPU's.       |

|-------|-------|-----------------------------------------------|

| U49-8 | 150ns | central SIO clock distributed to all DUART's. |

Multi Slave Product Reference Manual

Step 5: Memory Verification

Verify memory row and column addressing by monitoring pin 1 and pin 19 on each AM2965 memory driver circuit.

Step 6: Monitor Verification

Data Set Ready (J1-2, J3-2, J5-2) MUST be low for the monitor to issue a message to the console. Verify that the PS/NET-1 card is properly configured and connected to the Multi Slave, and that the terminal's baud rate is set to 9600. Ensure that the Multi Slave card is in a reset-hold condition by pressing the system reset button on the computer's front panel. Then, using a monitor program on the Master Processor, activate the desired slave CPU by issuing an OUT (slave command port),40H. The Multi Slave monitor should issue its logon message as described in Section 2 of this manual. Press any key on the slave console within two seconds after "un-resetting" it. The Multi Slave monitor should then be ready to accept commands.

STEP 7: Verification of other Major Components

Verification of other major Multi Slave components requires development of short software routines which will provide scope loops to support the analysis of Multi Slave signals some of the more commonly required routines have been incorporated in the Multi Slave Monitor program. These tests include memory and I/O read and write loops. See the monitor command list for further information.

\* 09× 10 \* I9× DE \* 09× ØZ

SECTION IV

#### THE MULTI SLAVE MONITOR

The Multi Slave contains a very powerful monitor program, providing numerous features not found in most simple monitors. Some of the highlights include:

- Full function decimal/hexadecimal calculator (expression evaluator)

- o 280 disassembler

- Offset variable for LIST and DUMP functions

- Comprehensive memory diagnostics

- Printer echo (all console input & output may be echoed to the printer) with user selectable baud rate

- Scope loops memory and I/O read/write loops

The basic monitor command structure is as follows:

COMMAND\_LETTER [V1 [,V2 [,V3]]] <CR>

where V1, V2, and V3 are variables (command parameters), and unless indicated otherwise, are hexadecimal values. Parameters may or may not be required depending upon the command. Note that ALL commands are terminated by a carriage return <CR>, and fields within brackets ([]) are optional.

#### MONITOR COMMANDS

- B BOOT this slave system by issuing an operating system download request to the master. For specific details about the download request program, see "Master/Slave Communications" in section II of this manual.

- C X1,X2,X3 COMPARE the contents of memory, starting at address X1 to address X2, for X3 bytes. If a mismatch occurs, the contents of both addresses will be displayed.

- D X1 [X2]] DUMP the contents of memory beginning at address OOOOH (if the DUMP command has not been previously invoked), or continue at the last address plus one, or at address X1 for 256 bytes (or thru address X2). SEE OFFSET (\$) COMMAND.

- F X1,X2,X3 FILL memory from address X1 thru X2 with data value X3.

- G X1 GO to address X1 (via a CALL) and execute the instructions at that address.

- H See the next subsection for details of this command.

- I X1 INPUT data from I/O port address X1 and display it on the console. To display the contents of the next sequential port, enter a carriage return; to display the contents of the prior port, enter a minus (-) sign.

- K [N1] Display the current bank number, or switch to bank N1.

- L [X1 [X2]] LIST, using Z80 mnemonics, the instructions beginning at address 0000H (if the LIST command has not been previously invoked), or continue at the last address plus one, or at address X1 for 18 lines of instructions, or thru address X2. SEE OFFSET (\$) COMMAND.

- M X1,X2,X3 MOVE the contents of memory beginning at address X1 thru address X2 to address X3.

- O X1.X2 OUTPUT data byte X2 to I/O port address X1.

- P (D1) Toggle the PRINTER online or offline, or set the printer baud rate to value D1 (decimal).

- S X1 SET the contents of address X1. The current contents of the memory location will be displayed. Enter KCR> to advance to the next address, (-) to go back to the prior address, two hexadecimal characters (0-9, A-F) to change the bex value, or (,A) to change the contents to ASCII value A.

- T [X1 [,X21] TEST memory beginning at 0000H thru the highest possible address (the starting address of the monitor -1), or starting at address X1 (thru address X2). A plus sign (+) will be displayed with each successful pass. Any address which fails will be displayed at the console, along with the expected and failing data pattern. Upon completion of the test (one complete pass at all specified addresses), the test will be terminated and a message will be displayed at the console.

- Z X1,X2 [,X3] Perform a Scope Loop test specified by function X1, as follows:

- 0 = Memory Read Loop

- 1 = Memory Write Loop

- 2 = I/O Read Loop

- 3 = I/O Write Loop

Field X2 is the memory address or I/O port address, and X3 is the data value to be written to the specified memory or I/O address. Note that field X3 is required only if the test function is a write operation.

S[X1] Display the current offset value, or change it to value X1. This offset will be added to the address specified in the DUMP and LIST commands.

#### MONITOR ASPECTS AND CONSIDERATIONS

The Multi Slave monitor takes two important factors into consideration; self preservation, and the possibility of an active master processor on the S-100 bus during monitor execution. Self preservation implies the protection of the memory region in which the monitor resides.

Interrupts are enabled while the monitor is executing; the interrupt service routine performs one important task, that of setting the SLAVE ALIVE bit at each 16.666 ms interrupt interval. This ensures that the master processor will not attempt to reset the slave; the slave always appears to be "alive."

Any command which modifies the contents of memory performs a test of the target addreas to ensure that it is not 1) the Z80 Mode 1 interrupt vector address or any portion of it (i.e. locations 0038H, 0039H or 003AH), and 2) an addreas within the monitor. In case 1, the SET, TEST, FILL and MOVE commands will simply skip over these locations. In case 2, an error message will be issued to the console.

There are two I/O address groups which must be accessed with care. The first group is 20H thru 2FH; an I/O read in this range asserts the SLAVE MESSAGE bit, indicating to the master processor that the slave is requesting service. Typically, this will initiate the operating system download sequence.

The second I/O address group is 70H thru 7FH, the "gateway" to the S-100 bus. An I/O read or write in this range causes the CPU to enter a WAIT condition, terminated only after the master has read from or written to the corresponding communications port. In most cases, this will be fatal to the monitor. To prevent an inadvertent read or write to these ports, the monitor will prompt with:

#### CONFIRM (Y/N):

when it encounters a read or write request to any one of the aforementioned addresses. A single keystroke reply is required, either 'Y' to perform the requested function, or any other key to terminate it.

#### OTHER FEATURES AND FACILITIES

The Multi Slave monitor provides a means of obtaining hardcopy output of all console I/O. When hardcopy output is desired, execution of the 'P' command will display the 'PRINTER ON' measage at the console, with all subsequent console I/O being echoed to the printer. The next invokation of the 'P' command terminates the printer output, and displays the 'PRINTER OFF' measage to the console.

The default printer baud rate is 9600 baud; this may be changed by using the second form of the 'P' command:

#### Pn <CR>

where 'n' is the desired baud rate. The baud rates currently supported are 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000, 2400, 4800, 7200, 9600, 19,200 and 38,400. There is one special case here, the 134.5 baud rate; this value should be entered as 134 (without the decimal fraction).

All monitor commands may be terminated with the ESC(ape) key. Console (and printer) output may be temporarily suspended by entering control-S (^S) and resumed by entering control-Q (^Q).

A monitor command line may be 'deleted' by entering control-X (^X). This causes the cursor to return to the beginning of the current line, immediately to the right of the asterisk (\*) prompt character. If hardcopy output is enabled, a carriage return/line feed/space sequence is issued to the printer so that the next command line is not typed over the current line.

All other control characters are invalid. The monitor will issue the bell character to the console in place of the control character.

All lower case characters entered on the console are converted to upper case.

THE 'H' COMMAND - EXPRESSION EVALUATOR

Pocket calculators with such capabilities as hexadecimal display and Boolean functions are a convenient tool, but when one ian't handy, such calculations by hand are tedious at best. For this reason, an expression evaluator has been included in the Multi Slave monitor program.

The expression evaluator has a total of 17 operators, as follows:

| 5.  | Dyadic AND                       |

|-----|----------------------------------|

| *   | Dyadic MULTIPLY                  |

| +   | Dyadic ADD or monadic PLUS       |

| -   | Dyadic SUBTRACT or monadic MINUS |

| 1   | Dyadic DIVIDE (two's complement) |

| 11  | Dyadic REMAINDER                 |

| <   | Dyadic LESS THAN                 |

| >   | Dyadic GREATER THAN              |

| < = | Dyadic LESS THAN OR EQUAL        |

| = = | Dyadic EQUAL                     |

| >=  | Dyadic GREATER THAN OR EQUAL     |

| <<  | Dyadic or monadic ROTATE LEFT    |

| >>  | Dyadic or monadic ROTATE RIGHT   |

| - I | Dyadic INCLUSIVE OR              |

| 1.1 | Dyadic EXCLUSIVE OR              |

| ~=  | Dyadic NOT EQUAL                 |

| ~   | Monadic NOT (one's complement)   |

Constants may occur in two forms, numbers or strings. Numbers may be in decimal or hexadecimal notation. A decimal number is simply a string of digits; a hexadecimal number is prefixed by either a dollar sign ( $\Rightarrow$ ) or enclosed in single quotes prefixed by an X (e.g.  $\Rightarrow$ FFFF or X'FFFF'). Expressions are evaluated to 16 bits of precision (modulo 65536, or  $\Rightarrow$ FFFF) using two's complement arithmetic, with no check for overflow. Strings are any sequence of characters enclosed in single quotes. Two consective single quotes are required to represent one single quote within a string. Null strings are ignored.

Expressions have the form:

[[OPERAND\_1 [OPERATOR]] OPERAND\_2

where OPERATOR is one of the aforementioned dyadic or monadic operators, and OPERAND\_1 and OPERAND\_2 are constants or expressions. Dyadic operators require both operands, monadic operators require only OPERAND\_2.

All operators have equal precedence, and expressions are evaluated from left to right. Parentheses around an expression may be used to alter precedence; the innermost expression in parenthesis is evaluated first.

The dyadic operators are used to form expressions which evaluate to either one or zero, indicating a true or false condition respectively. A true expression yields a result of one; a false comparsion produces a zero result.

The left and right rotation operators (<< and >>) perform a 16 bit rotate (not shift) operation; rotation implies wraparound of bits. Shifting can be accomplished with the multiply and divide operators. When used as monadic operators, operands are rotated one bit. When used as dyadic operators, the first operand specifies the number of bits to rotate.

If a string constant appears in an expression with operators, the value of the string is the ASCII code of the first character in the string. An exception to this rule occurs when two strings appear with a relational operator; then a character by character comparison of the two strings is performed, using the ASCII value to determine relative order. If the two strings are of unequal length, the shorter is padded on the right with spaces.

## EXAMPLES:

Expression -----3 (4) -(+3) ~3 9//8 1+2\*3 1+(2\*3) 5==5 \$FFFF<0 3+(2~=6) <<2 >>3 3>>\$FO 'A'+1

Evaluates to: \_\_\_\_\_\_ 3 4 ₽FFFD ₽FFFC 1 9 7 1 (indicates a true condition) 0 (\$FFFF=65535) 4 (3+1, where 1=true) 4 \$8001 \$001E \$0042

## S-100 BUS PINOUT

| S-100<br>Bus Pin | Mnemonic     | Active<br>State | Source           | Notes                          |

|------------------|--------------|-----------------|------------------|--------------------------------|

| 01               | +8 Volta     |                 | Bus              |                                |

| 02               | +16 Volts    |                 | Bus              |                                |

| 03               | XRDY         | High            | Slave            | Unused                         |

| 04               | VIO*         | -               | Slave            | Vectored Int 0                 |

| 05               | VI1*         |                 | Slave            | Vectored Int 1                 |

| 06               | VI2*         |                 | Slave            | Vectored Int 2                 |

| 07               | VI3*         |                 | Slave            | Vectored Int 3                 |

| 08               | VI4*         |                 | Slave            | Vectored Int 4                 |

| 09               | VI5*         |                 | Slave            | Vectored Int 5                 |

| 10               | VI6*         |                 | Slave            | Vectored Int 6                 |

| 11               | VI7*         |                 | Slave            | Vectored Int 7                 |

| 12               | NMI *        |                 | Slave            | Unused                         |

| 13               | PWRFAIL*     | Low             | Bus              | Unused                         |

| 14               | TMA3*        | Low (OC)        | Master           | Unused                         |

| 15               | A18          | High            | Maater           | Unused                         |

| 16               | A16          | High            | Master           | Unused                         |

| 17               | A17          | High            | Master           | Unused                         |

| 18               | SDSB*        | Low (OC)        | Master           | Unused                         |

| 19               | CDSB #       | Low (OC)        | Master           | Unused                         |

| 20               | GND          |                 | Bus              |                                |

| 21               |              |                 |                  | Unused                         |

| 22               | ADSB*        | Low (OC)        | Master           | Unused                         |

| 23               | DODSB×       | Low (OC)        | Master           | Unused                         |

| 24               | phi          | High            | Master           | Unused                         |

| 25               | pSTVAL*      | Low             | Master           | Unused                         |

| 26               | pHLDA        | High            | Master           | Unused                         |

| 27               |              |                 |                  | Unused                         |

| 28               |              |                 | <br>Ma - b a     | Unused                         |

| 29               | A05          | High            | Master           | Address bit 5<br>Address bit 4 |

| 30               | A04          | High            | Master           | Address bit 3                  |

| 31               | A03          | High            | Master           | Address bit 15                 |

| 32               | A15          | High            | Master<br>Master | Address bit 12                 |

| 33<br>34         | A12<br>A09   | High<br>High    | Master           | Unused                         |

|                  |              | High            | Master           | Data Out bit 1                 |

| 35               | DO1<br>DATA1 | High            | M/S              | Unused 1                       |

| 36               | DOO          | High            | Master           | Data Out bit O (LSB)           |

| 50               | DATAO        | High            | M/S              | Unused                         |

| 37               | A10          | High            | Master           | Unused                         |

| 38               | D04          | High            | Master           | Data Out bit 4                 |

| 00               | DATA4        | High            | M/S              | Unused                         |

| 39               | D05          | High            | Master           | Data Out bit 5                 |

|                  | DATA5        | High            | M/S              | Unused                         |

| 40               | D06          | High            | Master           | Data Out bit 6                 |

|                  | DATAG        | High            | M/S              | Unused                         |

| 41               | DI2          | High            | Slave            | Data In Bit 2                  |

| -                | DATA10       | High            | M/S              | Unused                         |

| 42               | DIG          | High            | Slave            | Data In bit 3                  |

|                  | DATA11       | High            | M/S              | Unused                         |

|                  |              |                 |                  |                                |

| S-100<br>Bua Pin | Mnemonic  | Active<br>State | Source | Notes                |

|------------------|-----------|-----------------|--------|----------------------|

| 43               | DI7       | High            | Slave  | Data In bit 7        |

| -10              | DATA15    | High            | M/S    | Unused               |

| 44               | aM1       | High            | Maater | Unused               |

| 45               | BOUT      | High            | Master | Output Bus Cycle     |

| 46               | aINP      | High            | Master | Input Bus Cycle      |

| 47               | BINF      | High            | Master | Unused               |

| 48               |           |                 |        | Unused (sHLTA)       |

| 49               | CLOCK     | High            | Master | Unused               |

| 50               | GND       |                 | Bus    | Ground               |

| 51               | +8 Volta  |                 | Bus    | di duna              |

| 52               | -16 Volta |                 | Bus    |                      |

| 53               | GND       |                 | Bus    | Ground               |

| 54               | SLV CLR*  | Low             | Master | Unused               |

| 55               | TMAO*     | Low (OC)        | Master | Unused               |

| 56               | TMA1 #    | Low (0C)        | Master | Unused               |

| 57               | TMA2*     | Low (OC)        | Master | Unused               |

| 58               | aXTRQ*    | Low             | Maater | Unused               |

| 59               | A19       | High            | Master | Unused               |

| 60               | SIXTN*    | Low (OC)        | Master | Unused               |

| 61               | A20       | High            | Master | Unused               |

| 62               | A21       | High            | Maater | Unused               |

| 63               | A22       | High            | Master | Unused               |

| 64               | A23       | High            | Master | Unused               |

| 65               |           |                 |        | Unused               |

| 66               |           |                 |        | Unused               |

| 67               |           |                 |        | Unused (PHANTOM*)    |

| 68               |           |                 |        | Unused (MWRT)        |

| 69               |           |                 |        | Unused               |

| 70               | GND       |                 | Bus    | Ground               |

| 71               |           |                 |        | Unused               |

| 72               | RDY       | High (OC)       | Slave  | Unused               |

| 73               | INT*      | Low (OC)        | Slave  | Unused               |

| 74               | HOLD*     | Low (OC)        | Master | Unused               |

| 75               | RESET *   | Low (OC)        | Bus    | System Reset         |

| 76               | pSYNC     | High            | Master | Bus Transfer control |

| 77               | pWR*      | Low             | Master | Data Bus Valid       |

| 78               | pDBIN     | High            | Master | Data In Strobe       |

| 79               | AO        | High            | Master | Address bit O (LSB)  |

| 80               | A1        | High            | Master | Address bit 1        |

| 81               | A2        | High            | Master | Address bit 2        |

| 82               | A6        | High            | Master | Address bit 6        |

| 83               | A7        | High            | Master | Address bit 7        |

| 84               | A8        | High            | Master | Unused               |

| 85               | A13       | High            | Master | Unused               |

| 86               | A14       | High            | Master | Unused               |

| 87               | A11       | High            | Master | Unused               |

| 88               | D02       | High            | Master | Data Out bit 2       |

|                  | DATA2     | High            | M/S    | Unused               |

| 89               | D03       | High            | Master | Data Out bit 3       |

|                  | DATA3     | High            | M/S    | Unused               |

| 90               | D07       | High            | Master | Data Out bit 7       |

|                  | DATA7     | High            | M/S    | Unused               |

|                  |           | •               |        |                      |

| S-100   |          | Active   |        |               |

|---------|----------|----------|--------|---------------|

| Bus Pin | Mnemonic | State    | Source | Notes         |

|         |          |          |        |               |

| 91      | DI4      | High     | Slave  | Data In bit 4 |

|         | DATA12   | High     | M/S    | Unuaed        |

| 92      | DI5      | High     | Slave  | Data In bit 5 |

|         | DATA13   | High     | M/S    | Unused        |

| 93      | DIG      | High     | Slave  | Data In bit 6 |

|         | DATA14   | High     | M/S    | Unused        |

| 94      | DI1      | High     | Slave  | Data In bit 1 |

|         | DATA9    | High     | M/S    | Unused        |

| 95      | DIO      | High     | Slave  | Data In bit O |

|         | DATA8    | High     | M/S    | Unused        |

| 96      | BINTA    | High     | Master | Unused        |

| 97      | aWO*     | Low      | Master | Unused        |

| 98      | ERROR #  | Low (OC) | Slave  | Unused        |

| 99      | POC*     | Low      | Bus    | Unused        |

| 100     | GND      |          | Bus    | Ground        |

(OC) = open collector Unused = pin not implemented on Multi Slave

## PROM SELECTION JUMPER BLOCKS

| 1 0 0 2        | PROM TYPE   | JUMPER        |

|----------------|-------------|---------------|

| 3004           |             |               |

| 5006           | 2716 (2K)   | 3-5, 4-6      |

| 7 0 0 8        | 2732 (4K)   | 5-7, 4-6      |

|                | 2764 (8K)   | 1-3, 5-7      |

| TYPICAL JUMPER | 27128 (16K) | 1-3, 6-8, 5-7 |

| BLOCK          | 27256 (32K) | 1-2, 6-8, 5-7 |

## S-100 BUS VECTORED INTERRUPT JUMPERS

|       | MULTI   | SLAV  | VE | JU   | IMPE | R BI | LOCI | к  | S-100 B | BUS  |     |

|-------|---------|-------|----|------|------|------|------|----|---------|------|-----|

|       |         |       |    |      |      |      |      | -  |         |      |     |

| Multi | Slave   | CPU   | 0  | 1 -  | - o  | o    |      | 2  | INTO*   | (pin | 4)  |

| **    | **      |       | •• | з -  | - o  | 0    |      | 4  | INT1 *  | (pin | 5)  |

| Multi | Slave   | CPU   | 1  | 5 -  | - o  | 0    |      | 6  | INT2*   | (pin | 6)  |

| ••    | ••      | ••    | •• | 7 -  | - 0  | 0    |      | 8  | INT3*   | (pin | 7)  |

| Multi | Slave   | CPU   | 2  | 9 -  | - o  | ٥    |      | 10 | INT4*   | (pin | 8)  |

| **    | ••      | ••    | •• | 11 - | - o  | 0    |      | 12 | INT5*   | (pin | 9)  |

| No    | o Conne | ectio | nc | 13 - | - 0  | 0    |      | 14 | INT6*   | (pin | 10) |

| ••    | •       | •     |    | 15 - | - 0  | 0    |      | 16 | INT7*   | (pin | 11) |

## BASE ADDRESS SELECTION

|     | (7) | (6) | (5)         | (4) |     |                                       |

|-----|-----|-----|-------------|-----|-----|---------------------------------------|

|     | Ī   | 1   | 5<br> <br>0 | I   |     |                                       |

| MSB |     |     |             |     | LSB | Address selection uses LOW TRUE LOGIC |

|     | 0   | 0   | 0           | 0   |     | (no jumper=1, jumpered=0) and repre-  |

|     | 1   | I   | ł           | 1   |     | sents the four most significant bits  |

|     | 2   | 4   | 6           | 8   |     | of the base address.                  |

Example:

| BASE ADDRESS | JUMPERS       |

|--------------|---------------|

|              |               |

| 70H          | 1-2           |

| 80H          | 3-4, 5-6, 7-8 |

| ЭОН          | 3-4, 5-6      |

| AOH          | 3-4, 7-8      |

| вон          | 3-4           |

| СОН          | 5-6, 7-8      |

| DOH          | 5-6           |

|              |               |

## Multi Slave Jumper Options

## SERIAL I/O CONNECTORS

| PIN NO. | SIGNAL N | AME                 | DIRECTION      |

|---------|----------|---------------------|----------------|

|         |          |                     |                |

| 1       | DCD      | Data Carrier Detect | input          |

| 2       | DSR      | Data Set Ready      | input          |

| * 3     | * * *    | see note below      | input/output   |

| 4       | RXD      | Receive Data        | input          |

| 5       | CTS      | Clear to Send       | input          |

| 6       | TXD      | Tranamit Data       | output         |

| 7       | RTS      | Request to Send     | output         |

| 8       | DTR      | Data Terminal Ready | output         |

| 9       | CLK      | Tx/Rx Clock         | input/output   |

| 10      | GND      | Signal Ground       | ground         |

| 11      | N/C      | •                   |                |

| 12      | +16 VDC  |                     | supply voltage |

| 13      | -16 VDC  |                     | supply voltage |

| 14      | +5 VDC   |                     | supply voltage |

|         |          |                     |                |

\* On channel A, this term is RNG (ring detect) and may be connected to the ring detect line on a modem. This line has no connected on channel B.

## I/O PORT ASSIGNMENTS

| ADDRESS (Hex) | TYPE | FUNCTION                                                             |

|---------------|------|----------------------------------------------------------------------|

| 00-0F         | R/W  | DUART Data/Control (see Signetics<br>2681 Documentation for details) |

| 10-1F         |      | Not Used                                                             |

| 20-2F         | R    | Asserts SLAVE MESSAGE bit                                            |

| 30-3F         | R    | De-asserts MASTER MESSAGE bit                                        |

| 40-4F         | ω    | BANK/PROM SELECT (details follow)                                    |

| 50-5F         | R    | STATUS PORT (MASTER and SLAVE bits)                                  |

| 60-6F         | R    | Asserts SLAVE ALIVE* bit                                             |

| 70-7F         | R/W  | S-100 DATA PORT                                                      |

.

## MULTI SLAVE SCHEMATICS

| Item     | Qty. | Part No.  | Description         | Reference                                                                           |

|----------|------|-----------|---------------------|-------------------------------------------------------------------------------------|

|          |      | 741 0067  |                     |                                                                                     |

| 1        | 5    | 74LS367   | BUS DRIVER          | U1,U47,U52,U53,U64                                                                  |

| 2<br>3   | 3    | 74LS590   | 8 BIT COUNTER       | U2,U6,U10                                                                           |

| 3<br>4   | 3    | SN2681    | DUART               | U5,U9,U18                                                                           |

|          | 6    | AM2965    | MEMORY DRIVER       | U13,U15,U17,U28,U31<br>U34                                                          |

| 5        | 3    | 280H      | CPU                 | U14,U16,U27                                                                         |

| 6        | 6    | 74LS138   | 3 TO 8 DECODER      | U29,U32,U41,U43,U44<br>U51                                                          |

| 7        | 3    | 74LS85    | 4 BIT COMPARATOR    | U30,U33,U42                                                                         |

| 8        | 3    | 74LS74    | DUAL D FLIP FLOP    | U39,U40,U58                                                                         |

| 9        | 3    | 74LS279   | QUAD LATCH          | U45,U56,U59                                                                         |

| 10       | 1    | 7406      | HEX INVERTER        | U46                                                                                 |

| 11       | 2    | 74LS00    | QUAD NAND GATE      | U49,U50                                                                             |

| 12       | З    | 74LS273   | OCTAL D FLIP FLOP   | U54,U55,U66                                                                         |

| 13       | 6    | 74LS373   | OCTAL LATCH         | U61,U62,U63,U68,U69<br>U70                                                          |

| 14       | 1    | 74LS393   | 4 BIT COUNTER       | U71                                                                                 |

| 15       | 1    | 74LS688   | 8 BIT ID COMPARATOR | U67                                                                                 |

| 16       | 1    | DS0026    | CLOCK DRIVER        | U57                                                                                 |

| 17       | з    | PAL16R4A  | PROG ARRAY LOGIC    | U21,U25,U37                                                                         |

| 18       | З    | PAL16L8A  | PROG ARRAY LOGIC    | U22,U26,U38                                                                         |

| 19       | 1    | PAL16L8   | PROG ARRAY LOGIC    | U60                                                                                 |

| 20       | З    | 2764JL25  | EPROM               | U19,U23,U35                                                                         |

| 21       | з    |           | 4.7K OHM PACK       | RP1,RP2,RP3                                                                         |

| 22       | 12   |           | 47 OHM 10% 1/4W     | R1-R12                                                                              |

| 23       | 1    |           | 1K 10% 1/4W         | R16                                                                                 |

| 24       | 5    |           | 10 OHM 10% 1/4W     | R17-R19,R21,R22                                                                     |

| 25       | 5    |           | 47 PF CAPACITOR     | C6-C10                                                                              |

| 26       | 1    |           | 5 PF CAPACITOR      | C11                                                                                 |

| 27       | 1    |           | 10 PF CAPACITOR     | C12                                                                                 |

| 28       | 1    |           | 100 PF CAPACITOR    | C13                                                                                 |

| 29       | 1    |           | 6.8 UF 25WVDC       | C2                                                                                  |

| 30       | з    |           | 10 UF 25WVDC        | C3-C5                                                                               |

| 31       | 1    |           | .1 UF CERAMIC CAP   | C1                                                                                  |

| 32       | 6    | TM4164EL9 | 64K x 8 SIP DRAM    | U3,U4,U7,U8,U11,U12                                                                 |

| 33       | 1    |           | 8 PIN DIP SOCKET    | U57                                                                                 |

| 34       | 8    |           | 14 PIN DIP SOCKET   | U39,U40,U46,U49, <b>U50</b><br>U58,U71,DL1                                          |

| 35       | 19   |           | 16 PIN DIP SOCKET   | U1,U2,U6,U10,U29,U30<br>U32,U33,U41,U42,U44,                                        |

| 36       | 23   |           | 20 PIN DIP SOCKET   | U45,U47,U51,U52,U53,<br>U56,U59,U64<br>U13,U15,U17,U21,U22,                         |

| 30       | 23   |           | 20 FIN DIF SOCKET   | U25,U26,U28,U31,U34,<br>U37,U38,U54,U55,U60,<br>U61,U62,U63,U66,U67,<br>U68,U69,U70 |

| 37       | 3    |           | 28 PIN DIP SOCKET   | 019,023,035                                                                         |

| 38       | 6    |           | 40 PIN DIP SOCKET   | U5,U9,U14,U16,U18,                                                                  |

| <u> </u> | 9    |           |                     | U27                                                                                 |

| 39       | 1    |           | 3.6864 MHz XTAL     | Y 1                                                                                 |

| 40       | 1    | NCTOSOC   | 8.00 MHz OSCILLATOR | Y2                                                                                  |

| 41       | 1    | DL6135    | SONE DELAY LINE     | DL1                                                                                 |

| -3 -4    | -    |           |                     |                                                                                     |

•

•

| Item       | Qty. | Part No. | Description         | Reference      |

|------------|------|----------|---------------------|----------------|

|            |      |          |                     |                |

| 42         | 6    |          | 14 PIN HEADER       | J1-J6          |

| 43         | 4    |          | 8 PIN HEADER        | E1-E8,E19-E26  |

|            |      |          |                     | E9,E16,E27-E34 |

| 44         | 1    |          | 16 PIN HEADER       | J <b>7</b>     |

| 45         | 1    | 78H05    | 5V/5A REGULATOR     | VR1            |

| <b>4</b> 6 | 2    |          | PCB EJECTORS        |                |

| 47         | 1    |          | HEAT SINK [REF VR1] |                |

| 48         | 2    |          | 6-32 x 3 SCREWS     |                |

| 49         | 2    |          | 6-32 NUTS           |                |

| 50         | 2    |          | #6 LOCK WASHER      |                |

Appendix G

-

### DESCRIPTION

interrupt driven system.

(DUART) is a single chip MOS-LSI com-

munications device that provides two in-

dependent full-duplex asynchronous

receiver transmitter channels in a single

package. It interfaces directly with micro-

processors and may be used in a polled or

The operating mode and data format of

each channel can be programmed inde-

pendently, Additionally, each receiver and

transmitter can select its operating speed

as one of eighteen fixed baud rates, a 16x

clock derived from a programmable

counter/timer, or an external 1x or 15x.

clock. The baud rate generator and

counterit mer can operate directly from a

crystal or from external clock inputs. The ability to independently program the

operating speed of the receiver and trans-

mitter make the DUART particularly attrac-

tive for dual-speed channel applications

Each receiver is quadruply buffered to

minimize the potential of receiver overrun.

or to reduce interrupt overhead in interrupt driven systems. In addition, a flow

control capability is provided to disable a

remote DUART transmitter when the buf-

Also provided on the SCN2681 are a multi-

purpose 7-bit input port and a multipur-

pose 8-bit output port. These can be used

as general purpose I/O ports or can be assigned specific functions such as clock

inputs or status/interrupt outputs) under

The SCN2681 is available in three package

versions to satisfy various system require-