# DLV11-J user's guide

EK-DLV1J-UG-001

digital equipment corporation • marlboro, massachusetts

#### Copyright © 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS |

|---------|--------------|---------|

| DEC     | DECSYSTEM-20 | OMNIBUS |

| PDP     | DIBOL        | OS/8    |

| DECUS   | EDUSYSTEM    | RSTS    |

| UNIBUS  | VAX          | RSX     |

|         | VMS          | IAS     |

# CONTENTS

# CHAPTER 1 INTRODUCTION

| 1.1   | INTRODUCTION                         | 1-1 |

|-------|--------------------------------------|-----|

| 1.2   | SPECIFICATIONS                       | 1-2 |

| 1.2.1 | Electrical                           | 1-2 |

| 1.2.2 | Environmental                        | 1-3 |

| 1.2.3 | Physical                             | 1-3 |

| 1.2.4 | Module Contact Finger Identification |     |

| 1.2.5 | Backplane Pinning Utilization        | 1-3 |

| 1.3   | OPTIONS                              |     |

| 1.3.1 | Cables                               | 1-3 |

| 1.3.2 | DLV11-KA 20 mA Current Loop Option   | 1-5 |

# CHAPTER 2 INSTALLATION

| 2.1     | INTRODUCTION                               |      |

|---------|--------------------------------------------|------|

| 2.2     | CONFIGURING MODULE JUMPERS                 |      |

| 2.2.1   | General                                    |      |

| 2.2.2   | Addressing                                 |      |

| 2.2.2.1 | Device Register Addresses                  |      |

| 2.2.2.2 | Interrupt Vectors                          | 2-8  |

| 2.2.2.3 | Console Device Jumpers                     |      |

| 2.2.3   | Configuring Channel Word Formats           | 2-12 |

| 2.2.3.1 | General                                    | 2-12 |

| 2.2.3.2 | Number of Data Bits                        | 2-12 |

| 2.2.3.3 | Number of STOP Bits                        | 2-12 |

| 2.2.3.4 | Parity Inhibit                             | 2-12 |

| 2.2.4   | Baud Rate                                  | 2-14 |

| 2.2.5   | Channel 3 BREAK Response                   | 2-15 |

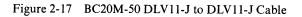

| 2.2.6   | Serial Line Signal Level Compatibility     | 2-16 |

| 2.2.6.1 | General                                    | 2-16 |

| 2.2.6.2 | EIA RS-422                                 | 2-17 |

| 2.2.6.3 | EIA RS-423 and RS-232C                     | 2-17 |

| 2.2.6.4 | Slew Rates                                 | 2-17 |

| 2.2.6.5 | 20 mA Current Loop                         | 2-18 |

| 2.3     | INSTALLATION                               |      |

| 2.3.1   | Module Installation                        | 2-18 |

| 2.3.1.1 | Module Contact Finger (Pin) Identification | 2-18 |

| 2.3.1.2 | Module Priority                            | 2-19 |

| 2.3.2   | Cabling Considerations                     | 2-21 |

iii

# CONTENTS (Cont)

| 2.3.3.1       Modem Operating Cabling.       2-22         2.3.3.2       Local Terminal Operation Cable.       2-22         2.3.3.3       DLVI1-J to DLVI1-Operation Cabling.       2-22         2.3.3.4       DLVI1-J to SLU Module Cabling.       2-22         2.4       CHECKOUT/ACCEPTANCE TESTS       2-22         CHAPTER 3       PROGRAMMING       3-1         3.1       GENERAL       3-1         3.2       DEVICE REGISTER ADDRESSING       3-1         3.3       INTERRUPT VECTORS       3-2         3.4       WORD FORMATS       3-2         3.5       INTERRUPTS       3-2         3.6       CONSOLE DEVICE       3-5         CHAPTER 4       TECHNICAL DESCRIPTION       4-1         4.1       GENERAL       4-1         4.2       MODULE FUNCTIONS       4-4         4.3       BUS INTERFACE       4-4         4.3.1       BUS INTERFACE       4-4         4.3.2       Address Comparison       4-5         4.3.3       Channel 3 Console Device Addressing       4-6         4.4.4       Notel Device Generation       4-6         4.4.4       Notel Device Generation       4-6         4.4.4       Notel D                                               | 2.3.3     | Cable Installation                    | 2-22 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|------|

| 2.3.3.2       Local Terminal Operation Cable.       2-22         2.3.3.3       DLV11-J to DLV11-J Operation Cabling.       2-22         2.3.3.4       DLV11-J to SLU Module Cabling.       2-22         2.4       CHECKOUT/ACCEPTANCE TESTS       2-22         CHAPTER 3       PROGRAMMING       3-1         3.1       GENERAL       3-1         3.2       DEVICE REGISTER ADDRESSING.       3-1         3.3       INTERRUPT VECTORS.       3-2         3.4       WORD FORMATS       3-2         3.5       INTERRUPTS.       3-2         3.6       CONSOLE DEVICE       3-5         CHAPTER 4       TECHNICAL DESCRIPTION       4-1         4.1       GENERAL       4-1         4.2       MODULE FUNCTIONS.       4-1         4.3       BUS INTERFACE       4-4         4.3.1       BUS INTERFACE       4-4         4.3.2       Address Comparison       4-5         4.3.3       Channel 3 Console Device Addressing       4-6         4.4.1       Interrupt Achowledge Detection       4-6         4.3.4       Vector Transmission       4-6         4.4.2       Interrupt Request Generation       4-6         4.4.3       <                                           | 2.3.3.1   | Modem Operating Cabling               | 2-22 |

| 2.3.3.3       DLVII-J to DLVII-J Operation Cabling.       2-22         2.3.3.4       DLVII-J to SLU Module Cabling.       2-22         2.4       CHECKOUT/ACCEPTANCE TESTS       2-22         CHAPTER 3       PROGRAMMING       3-1         3.1       GENERAL       3-1         3.2       DEVICE REGISTER ADDRESSING.       3-1         3.3       INTERRUPT VECTORS.       3-2         3.4       WORD FORMATS       3-2         3.5       INTERRUPTS.       3-2         3.6       CONSOLE DEVICE       3-5         CHAPTER 4       TECHNICAL DESCRIPTION         4.1       GENERAL       4-1         4.2       MODULE FUNCTIONS.       4-1         4.3       BUS INTERFACE       4-4         4.3.1       Bus Interfacing       4-4         4.3.2       Address Comparison       4-6         4.3.4       Vector Tramsission       4-6         4.3.4       Vector Transmission       4-6         4.4       INTERRUPT AND VECTOR GENERATION LOGIC       4-6         4.4.1       Interrupt Request Generation       4-6         4.4.2       Interrupt Request Generation       4-6         4.4.3       Vector Generation <td< td=""><td>2.3.3.2</td><td></td><td></td></td<> | 2.3.3.2   |                                       |      |

| 2.3.3.4DLV11-J to SLU Module Cabling2-222.4CHECKOUT/ACCEPTANCE TESTS2-22CHAPTER 3PROGRAMMING3.1GENERAL3-13.2DEVICE REGISTER ADDRESSING3-13.3INTERRUPT VECTORS3-23.4WORD FORMATS3-23.5INTERRUPTS3-23.6CONSOLE DEVICE3-5CHAPTER 4TECHNICAL DESCRIPTION4.1GENERAL4-14.2MODULE FUNCTIONS4-14.3BUS INTERFACE4-44.3.1Bus Interfacing4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4Interrupt Request Generation4-64.4.4Board Initialization4-74.5ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-94.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.7.4ReGISTER LOGIC4-94.7.5ADDRESS LATCH4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.7.4Generation4-144.9.1Generation4-144.9.2Receiver Operations4-144.9.1Generation4-144.9.2Receiver Operation                                                                                                                                                                                                                                                                                               | 2.3.3.3   |                                       |      |

| 2.4       CHECKOUT/ACCEPTANCE TESTS       2-22         CHAPTER 3       PROGRAMMING         3.1       GENERAL       3-1         3.2       DEVICE REGISTER ADDRESSING       3-1         3.3       INTERRUPT VECTORS       3-2         3.4       WORD FORMATS       3-2         3.5       INTERRUPTS       3-2         3.6       CONSOLE DEVICE       3-5         CHAPTER 4       TECHNICAL DESCRIPTION       4-1         4.1       GENERAL       4-1         4.2       MODULE FUNCTIONS       4-1         4.3       BUS INTERFACE       4-4         4.3.1       Bus Interfacing       4-4         4.3.2       Address Comparison       4-5         4.3.3       Channel 3 Console Device Addressing       4-6         4.4       INTERRUPT AND VECTOR GENERATION LOGIC       4-6         4.4       Interrupt Acknowledge Detection       4-6         4.4.4       Board Initialization       4-7         4.5       ADDRESS COMPARE       4-7         4.6       ADDRESS COMPARE       4-7         4.7       Interrupt Operations       4-9         4.7.1       Interrupt Operations       4-9                                                                                  | 2.3.3.4   | DLV11-J to SLU Module Cabling         | 2-22 |

| 3.1       GENERAL       3-1         3.2       DEVICE REGISTER ADDRESSING       3-1         3.3       INTERRUPT VECTORS       3-2         3.4       WORD FORMATS       3-2         3.5       INTERRUPTS       3-2         3.6       CONSOLE DEVICE       3-5         CHAPTER 4       TECHNICAL DESCRIPTION       4-1         4.1       GENERAL       4-1         4.2       MODULE FUNCTIONS       4-1         4.3       BUS INTERFACE       4-4         4.3.1       Bus Interfacing       4-4         4.3.2       Address Comparison       4-5         4.3.3       Channel 3 Console Device Addressing       4-6         4.3.4       Vector Transmission       4-6         4.4       Interrupt Request Generation       4-6         4.4.1       Interrupt Request Generation       4-6         4.4.2       Interrupt Acknowledge Detection       4-6         4.4.4       Board Initialization       4-7         4.5       ADDRESS COMPARE       4-7         4.6       ADDRESS COMPARE       4-7         4.7       I/O CONTROL LOGIC       4-8         4.7.1       Interrupt Operations       4-9                                                                          | 2.4       | CHECKOUT/ACCEPTANCE TESTS             | 2-22 |

| 3.2       DEVICE REGISTER ADDRESSING.       3-1         3.3       INTERRUPT VECTORS.       3-2         3.4       WOR DFORMATS.       3-2         3.5       INTERRUPTS.       3-2         3.6       CONSOLE DEVICE       3-5         CHAPTER 4       TECHNICAL DESCRIPTION         4.1       GENERAL       4-1         4.2       MODULE FUNCTIONS.       4-1         4.3       BUS INTERFACE       4-4         4.3.1       BUS INTERFACE       4-4         4.3.2       Address Comparison       4-5         4.3.3       Channel 3 Console Device Addressing       4-6         4.4.4       Interrupt Request Generation       4-6         4.4.1       Interrupt Acknowledge Detection       4-6         4.4.2       Interrupt Acknowledge Detection       4-6         4.4.3       Vector Generation       4-6         4.4.4       Board Initialization       4-7         4.5       ADDRESS LATCH       4-8         4.7       I/O CONTROL LOGIC       4-8         4.7.1       Interrupt Operations       4-9         4.7.3       Output Operations       4-9         4.7.4       BOARESS LATCH       4-8                                                                    | CHAPTER 3 | PROGRAMMING                           |      |

| 3.3INTERRUPT VECTORS.3-23.4WORD FORMATS.3-23.5INTERRUPTS.3-23.6CONSOLE DEVICE.3-5CHAPTER 4TECHNICAL DESCRIPTION4.1GENERAL.4-14.2MODULE FUNCTIONS.4-14.3BUS INTERFACE.4-44.3.1BUS INTERFACE.4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing.4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-64.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.7.4REGISTER LOGIC4-94.8REGISTER LOGIC4-94.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER4-144.9.1General4-144.9.2Receiver Operation4-144.9.2Ferro Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.1       |                                       |      |

| 3.4WORD FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.2       |                                       |      |

| 3.5INTERRUPTS3-23.6CONSOLE DEVICE3-5CHAPTER 4TECHNICAL DESCRIPTION4.1GENERAL4-14.2MODULE FUNCTIONS4-14.3BUS INTERFACE4-44.3.1Bus Interfacing4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.3Vector Transmission4-74.5ADDRESS COMPARE4-74.6ADDRESS COMPARE4-74.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8REGISTER LOGIC4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.3       | INTERRUPT VECTORS                     | 3-2  |

| 3.6       CONSOLE DEVICE       .3-5         CHAPTER 4       TECHNICAL DESCRIPTION       4-1         4.1       GENERAL       4-1         4.2       MODULE FUNCTIONS       4-1         4.3       BUS INTERFACE       4-4         4.3.1       Bus Interfacing       4-4         4.3.2       Address Comparison       4-5         4.3.3       Channel 3 Console Device Addressing       4-6         4.4.4       INTERRUPT AND VECTOR GENERATION LOGIC       4-6         4.4.1       Interrupt Acknowledge Detection       4-6         4.4.1       Interrupt Acknowledge Detection       4-6         4.4.3       Vector Generation       4-6         4.4.4       Board Initialization       4-7         4.5       ADDRESS LATCH       4-8         4.7       I/O CONTROL LOGIC       4-8         4.7.1       Interrupt Operations       4-9         4.7.2       Input Operation       4-9         4.7.3       Output Operations       4-9         4.7.4       General       4-10         4.9       UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER       4-14         4.9.1       General       4-14         4.9.2       Receiver Ope                                               | 3.4       | WORD FORMATS                          | 3-2  |

| CHAPTER 4TECHNICAL DESCRIPTION4.1GENERAL4-14.2MODULE FUNCTIONS4-14.3.1Operational Overview4-14.3.2Address Comparison4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-154.9.2Receiver Operation4-154.9.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.5       | INTERRUPTS                            | 3-2  |

| 4.1GENERAL4-14.2MODULE FUNCTIONS4-14.2.1Operational Overview4-14.3BUS INTERFACE4-44.3.1Bus Interfacing4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.7.4CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.6       | CONSOLE DEVICE                        | 3-5  |

| 4.2MODULE FUNCTIONS.4-14.2.1Operational Overview.4-14.3BUS INTERFACE.4-44.3.1Bus Interfacing.4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing.4-64.3.4Vector Transmission.4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation.4-64.4.2Interrupt Acknowledge Detection.4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS COMPARE4-74.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8REGISTER LOGIC4-144.9.1General4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CHAPTER 4 | TECHNICAL DESCRIPTION                 |      |

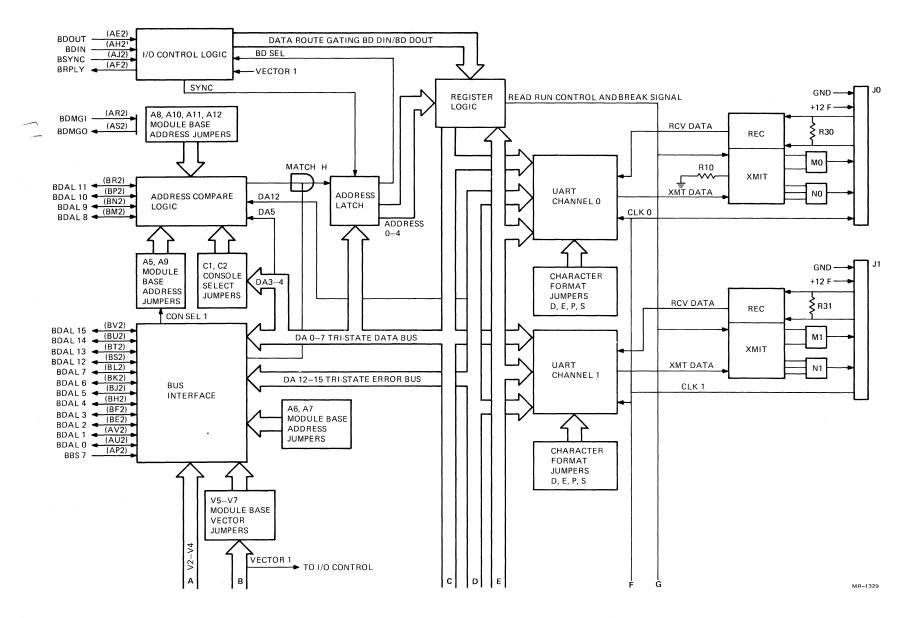

| 4.2.1Operational Overview.4-14.3BUS INTERFACE.4-44.3.1Bus Interfacing4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing.4-64.3.4Vector Transmission.4-64.4INTERRUPT AND VECTOR GENERATION LOGIC.4-64.4.1Interrupt Request Generation.4-64.4.2Interrupt Acknowledge Detection.4-64.4.3Vector Generation.4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH.4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8REGISTER LOGIC4-144.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER4-14(UART) OPERATION4-144.9.1General.4-154.9.2Receiver Operation4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.1       | GENERAL                               | 4-1  |

| 4.3BUS INTERFACE4-44.3.1Bus Interfacing4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8REGISTER LOGIC4-144.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER4-14(UART) OPERATION4-144.9.1General4-154.9.2Receiver Operation4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.2       | MODULE FUNCTIONS                      | 4-1  |

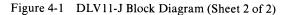

| 4.3.1Bus Interfacing4-44.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing4-64.3.4Vector Transmission4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8REGISTER LOGIC4-144.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER(UART) OPERATION(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.92.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.2.1     | Operational Overview                  | 4-1  |

| 4.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing4-64.3.4Vector Transmission4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER4-14(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.92.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.3       | BUSINTERFACE                          | 4-4  |

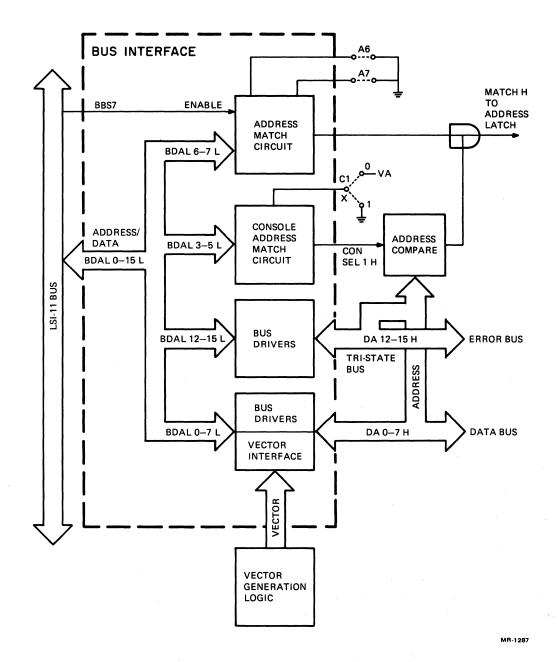

| 4.3.2Address Comparison4-54.3.3Channel 3 Console Device Addressing4-64.3.4Vector Transmission4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operation4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER4-14(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.92.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.3.1     | Bus Interfacing                       | 4-4  |

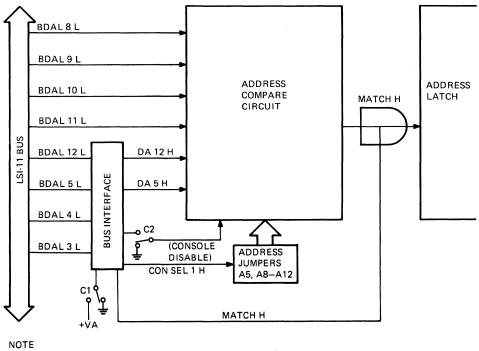

| 4.3.3Channel 3 Console Device Addressing4-64.3.4Vector Transmission4-64.4INTERRUPT AND VECTOR GENERATION LOGIC4-64.4.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER4-144.9.1General4-144.9.2Receiver Operation4-154.9.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.3.2     |                                       |      |

| 4.3.4Vector Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.3.3     |                                       |      |

| 44.1Interrupt Request Generation4-64.4.2Interrupt Acknowledge Detection4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.3.4     |                                       |      |

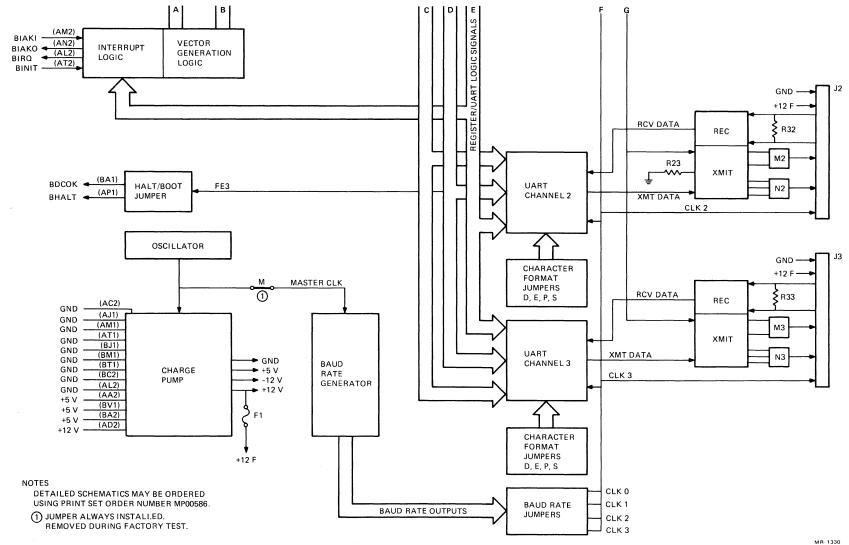

| 4.4.2Interrupt Acknowledge Detection.4-64.4.3Vector Generation.4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.4       | INTERRUPT AND VECTOR GENERATION LOGIC |      |

| 4.4.2Interrupt Acknowledge Detection4-64.4.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.4.1     | Interrupt Request Generation          |      |

| 44.3Vector Generation4-64.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8REGISTER LOGIC4-94.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.4.2     |                                       |      |

| 4.4.4Board Initialization4-74.5ADDRESS COMPARE4-74.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operations4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8REGISTER LOGIC4-94.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.4.3     |                                       |      |

| 4.6ADDRESS LATCH4-84.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operation4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.4.4     |                                       |      |

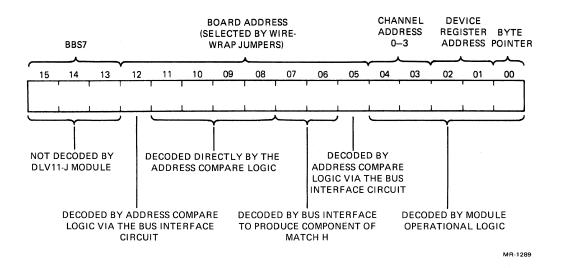

| 4.7I/O CONTROL LOGIC4-84.7.1Interrupt Operations4-94.7.2Input Operation4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.5       | ADDRESS COMPARE                       |      |

| 4.7.1Interrupt Operations4-94.7.2Input Operation4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.1.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.6       | ADDRESS LATCH                         | 4-8  |

| 4.7.1Interrupt Operations4-94.7.2Input Operation4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.1.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.7       | I/O CONTROL LOGIC                     | 4-8  |

| 4.7.2Input Operation4-94.7.3Output Operations4-94.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.7.1     |                                       |      |

| 4.7.3Output Operations4-94.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.7.2     |                                       |      |

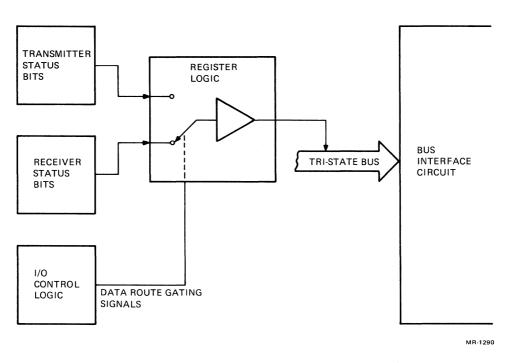

| 4.8REGISTER LOGIC4-94.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.7.3     |                                       |      |

| 4.8.1CSR Data Flow4-104.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION4-144.9.1General4-144.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                       |      |

| 4.9UNIVERSAL ASYNCHRONOUS RECEIVE TRANSMITTER<br>(UART) OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                       |      |

| (UART) OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                       |      |

| 4.9.1       General       4-14         4.9.2       Receiver Operation       4-15         4.9.2.1       Error Detection       4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                       | 4-14 |

| 4.9.2Receiver Operation4-154.9.2.1Error Detection4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.9.1     |                                       |      |

| 4.9.2.1 Error Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                       |      |

| $\omega$ $\gamma$ $\gamma$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                       |      |

# **CONTENTS** (Cont)

# Page

| 4.9.2.3 | Overrun Error (OE)       | 4-16 |

|---------|--------------------------|------|

| 4.9.2.4 | Parity Error (PE)        |      |

| 4.9.2.5 | Error Flag               |      |

| 4.9.3   | Character Formatting     |      |

| 4.9.4   | Transmit Operation       |      |

| 4.10    | BREAK LOGIC              |      |

| 4.11    | BAUD RATE CONTROL        | 4-18 |

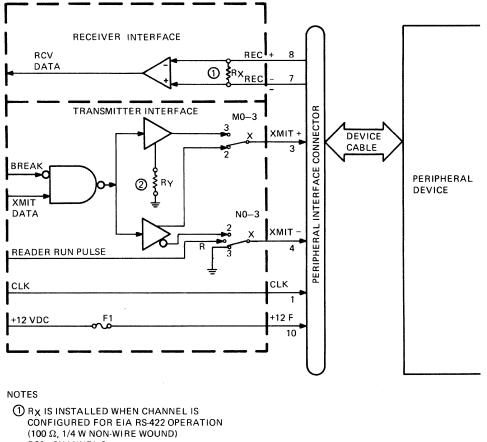

| 4.12    | PERIPHERAL INTERFACE     | 4-18 |

| 4.13    | DC-TO-DC POWER CONVERTER |      |

|         |                          |      |

# APPENDIX A DLV11-KA USER'S GUIDE

# **FIGURES**

# Figure No.

## Title

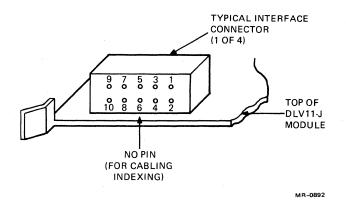

| 1-1  | DLV11-J Connector Pinning                                       | 1-2  |

|------|-----------------------------------------------------------------|------|

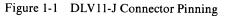

| 1-2  | Module Contact Finger Identification                            | 1-4  |

| 1-3  | DLV11-J Cabling Summary                                         | 1-5  |

| 1-4  | DLV11-J 20 mA Cabling Summary                                   | 1-6  |

| 2-1  | DLV11-J Component and Jumper Factory Configuration Summary      | 2-2  |

| 2-2  | Device Register Address Format                                  |      |

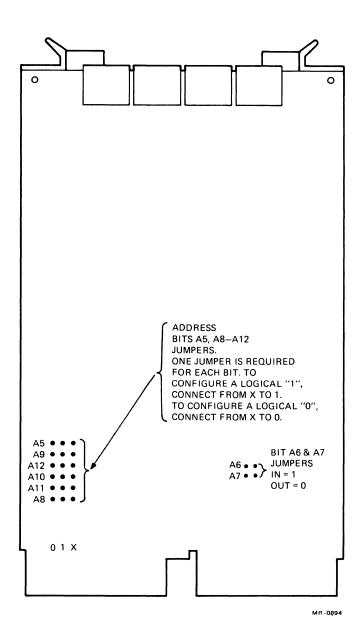

| 2-3  | Device Register Address Jumper Locations                        | 2-5  |

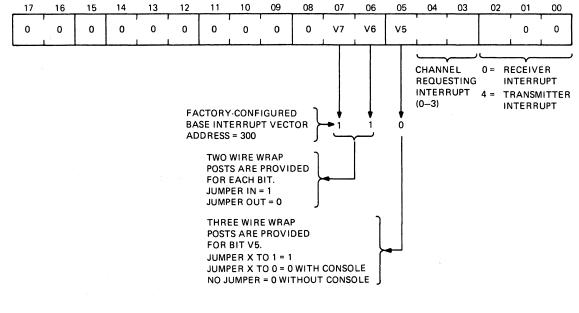

| 2-4  | Interrupt Vector Format                                         |      |

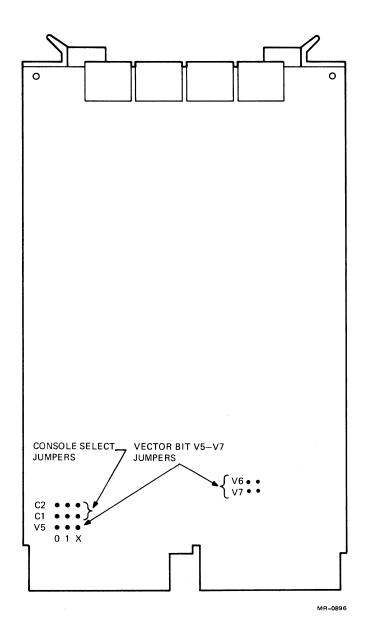

| 2-5  | Interrupt Vector Address and Console Select Jumper Locations    | 2-9  |

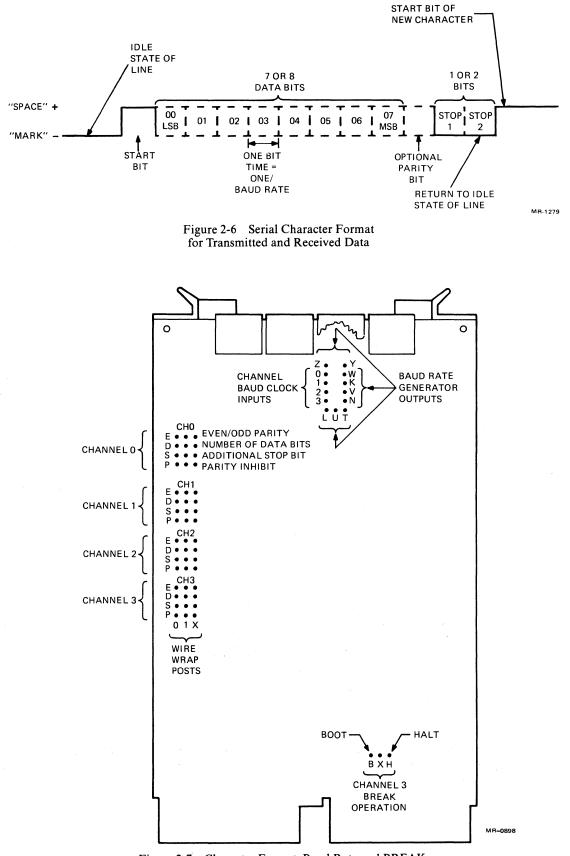

| 2-6  | Serial Character Format for Transmitted and Received Data       | 2-13 |

| 2-7  | Character Format, Baud Rate and BREAK Response Jumper Locations | 2-13 |

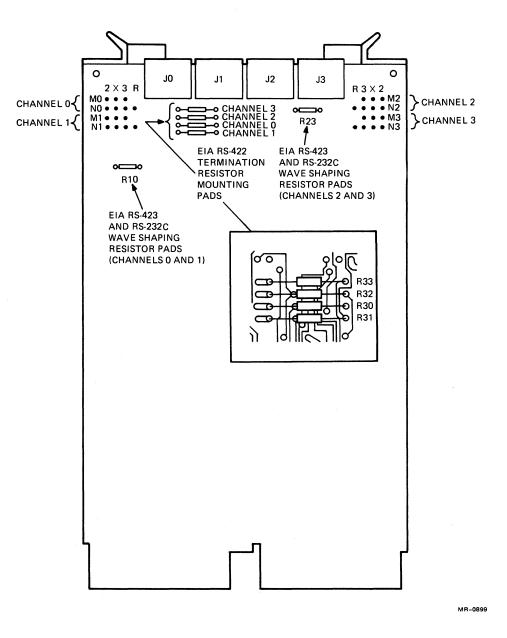

| 2-8  | Serial Channel Signal Level Jumpers and Pads                    | 2-16 |

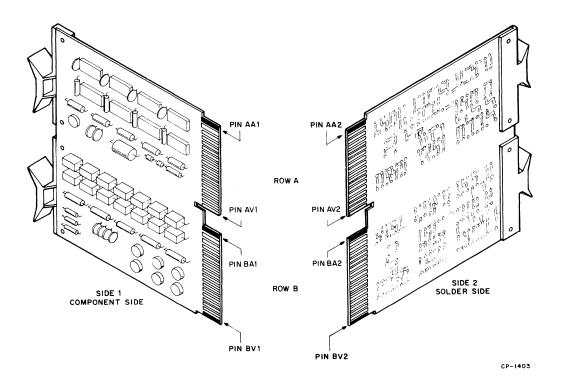

| 2-9  | Module Contact Finger Identification                            | 2-19 |

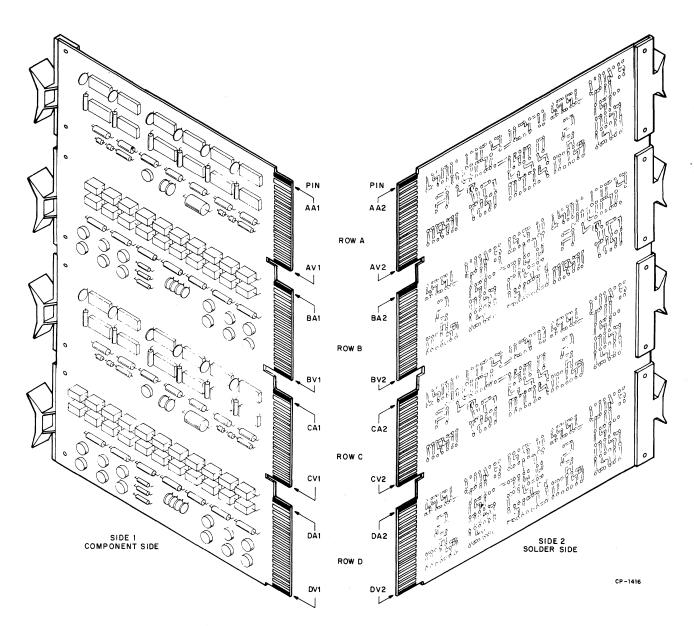

| 2-10 | Quad Module Contact Finger Identification                       | 2-20 |

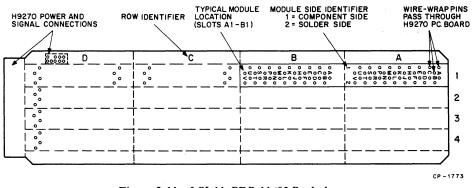

| 2-11 | LSI-11, PDP-11/03 Backplane Module Pin Identification           | 2-20 |

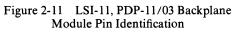

| 2-12 | Baud Rate vs Cable Length                                       | 2-21 |

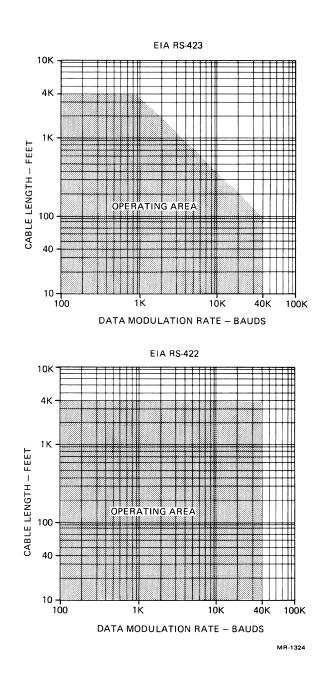

| 2-13 | DLV11-J Cabling Summary                                         | 2-24 |

| 2-14 | BC21B-05 Peripheral Device Cable                                | 2-25 |

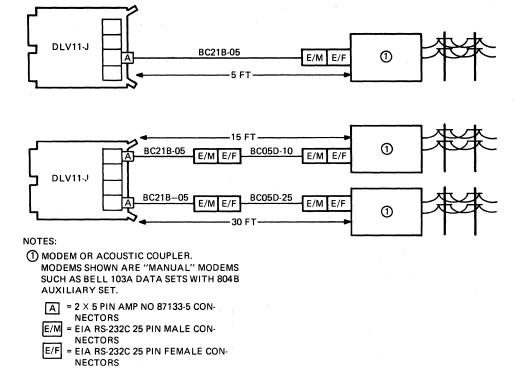

| 2-15 | DLV11-J to Modem or Acoustic Coupler                            | 2-26 |

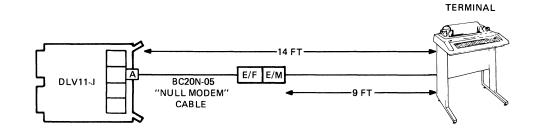

| 2-16 | Local Terminal Cabling                                          | 2-27 |

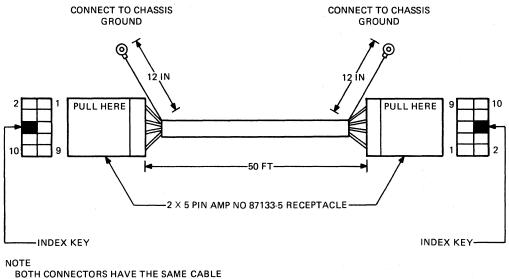

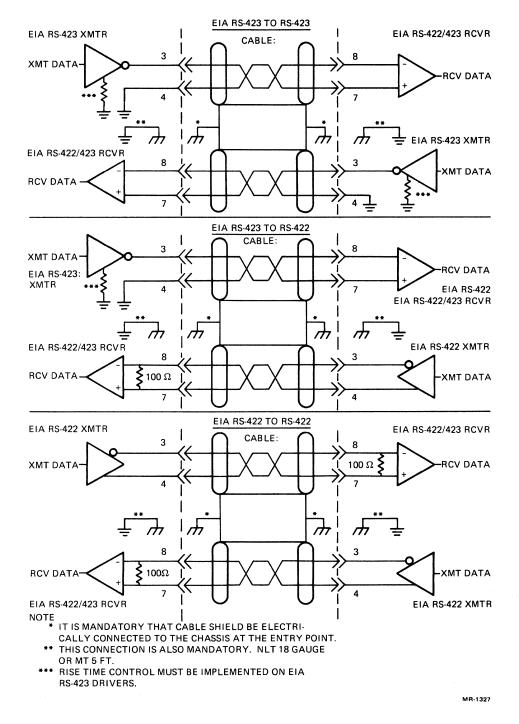

| 2-17 | BC20M-50 DLV11-J to DLV11-J Cable                               | 2-28 |

| 2-18 | Cable Construction for DLV11-J to DLV11-J Operation             | 2-29 |

| 2-19 | DLV11-J to SLU Module Cabling                                   | 2-30 |

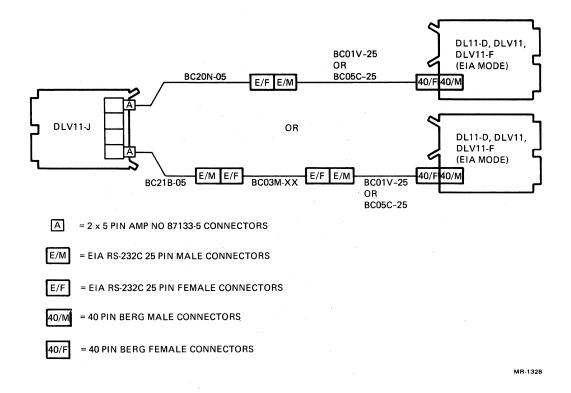

| 3-1  | DLV11-J Device Register Word Format                             | 3-3  |

| 4-1  | DLV11-J Block Diagram                                           | 4-2  |

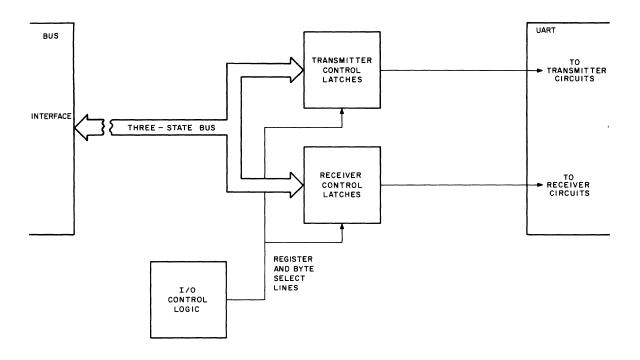

| 4-2  | DLV11-J Data Flow, Simplified Block Diagram                     | 4-4  |

# FIGURES (Cont)

# Figure No.

# Title

# Page

| 4-3  | Bus Interface Signal Flow                    | 4-5  |

|------|----------------------------------------------|------|

| 4-4  | Address Compare Circuit Block Diagram        |      |

| 4-5  | Summary of Board Address Decoding            |      |

| 4-6  | Control/Status Register During DATI          |      |

| 4-7  | Control/Status Register During DATO or DATOB |      |

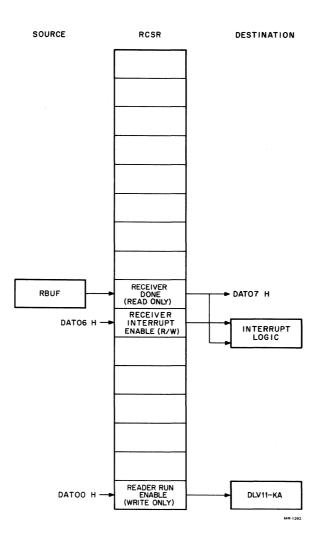

| 4-8  | DLV11-J RCSR Data Flow                       | 4-12 |

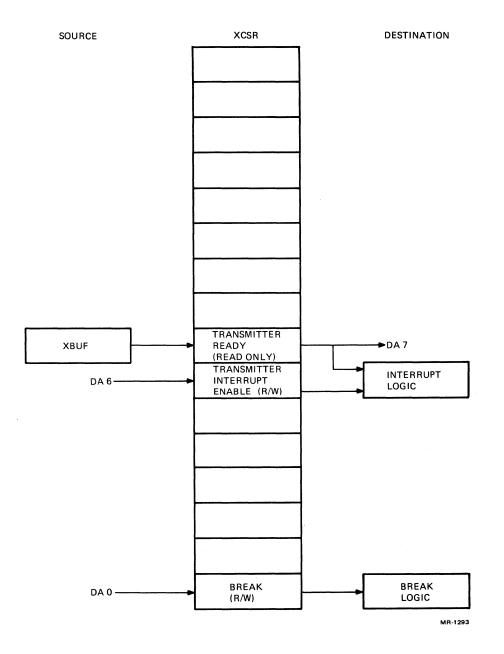

| 4-9  | DLV11-J XCSR Data Flow                       |      |

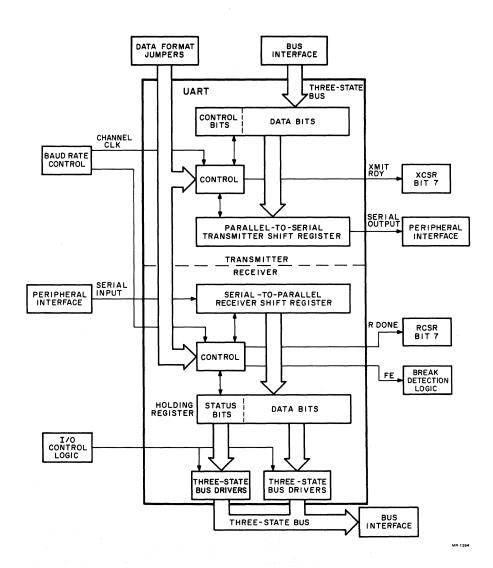

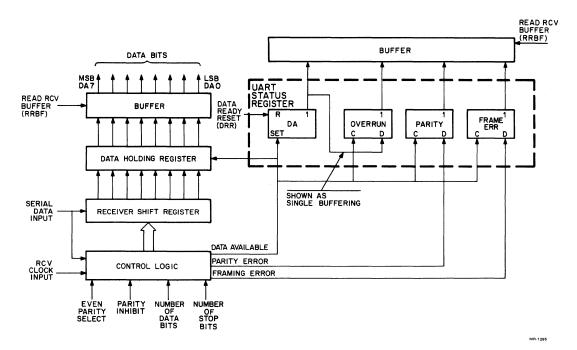

| 4-10 | UART Signal Flow (Typical for All Channels)  | 4-14 |

| 4-11 | UART Receiver Block Diagram                  |      |

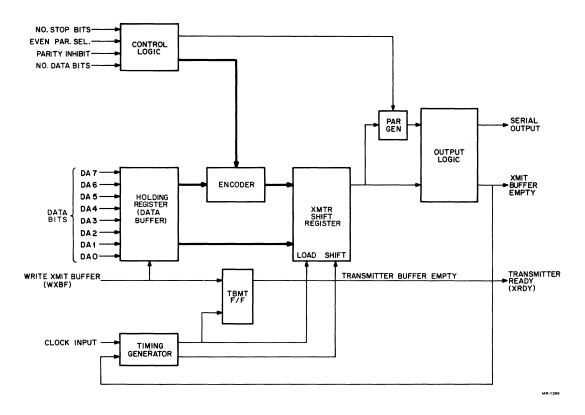

| 4-12 | UART Transmitter Block Diagram               | 4-17 |

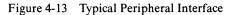

| 4-13 | Typical Peripheral Interface                 |      |

# **TABLES**

## Table No.

## Title

| 1-1  |   | DLV11-J Connector Pinning Description                                   | 1-2  |

|------|---|-------------------------------------------------------------------------|------|

| 1-2  |   | Backplane Pin Utilization                                               | 1-4  |

| 2-1  |   | DLV11-J Component and Jumper Factory Configuration Summary              | 2-3  |

| 2-2  |   | General Device Register Address Assignments (Without console selected)  | 2-6  |

| 2-3  |   | Specific Device Register Address Assignments (DLV11-J configured        |      |

|      |   | with $BA = 176500$ and $BV = 300$ without console selected)             | 2-6  |

| 2-4  |   | General Device Register Address Assignments (General configuration      |      |

|      |   | with console selected)                                                  | 2-7  |

| 2-5  |   | Specific Device Register Address Assignments (Factory configuration     |      |

|      |   | with $BA = 176500$ , $BV = 300$ and console enabled)                    | 2-7  |

| 2-6  |   | General Vector Assignments (Without console selected)                   | 2-9  |

| 2-7  |   | Specific Vector Assignments (DLV11-J configured with $BV = 300$ without |      |

|      |   | console selected)                                                       | 2-10 |

| 2-8  |   | General Vector Assignments (With console selected)                      | 2-10 |

| 2-9  |   | Specific Vector Assignments (Factory-configured with $BV = 300$ with    |      |

|      |   | console selected)                                                       | 2-10 |

| 2-10 |   | Summary of Vector Jumper Configurations                                 | 2-11 |

| 2-11 |   | Summary of Console Selection Jumper Configurations                      | 2-12 |

| 2-12 |   | Summary of Character Format Jumper Configurations                       |      |

| 2-13 |   | Baud Rate Generator Outputs                                             | 2-15 |

| 2-14 |   | Channel 3 BREAK Operation Jumper Summary                                |      |

| 2-15 |   | Summary of Serial Channel Signal Level Compatibility Configurations     | 2-17 |

| 2-16 | , | EIA RS-423 and RS-232C Wave-Shaping Resistor Values                     | 2-18 |

| 2-17 |   | Definition of Cables                                                    |      |

| 3-1  |   | DLV11-J Word Formats                                                    | 3-4  |

# CHAPTER 1 INTRODUCTION

#### **1.1 INTRODUCTION**

This manual contains all user information required for installing, interfacing, and programming the DLV11-J 4-Channel Asynchronous Serial Line Unit (SLU) Interface.

The DLV11-J is an LSI-11 bus-compatible interface module (M8043) that contains four asynchronous serial line channels. Serial line channels can be independently configured for Electronics Industry Association (EIA) RS-422, RS-423, or RS-232C signal compatibility. Provisions are also made for configuring the channels for 20 mA current loop (and "reader run") via the DLV11-KA 20 mA option (described in Appendix A). Each DLV11-J module has the following features:

- Four independent serial line interfaces exist with consecutive bus device address and vector assignments that can be user-configured for system requirements.

- Each channel can be independently configured for any of the following selections.

Crystal-Controlled Baud Rates -150, 300, 600, 1200, 2400, 4800, 9600, 19200, or 38400 bits per second (bits/s) -110 bits/s is available when the DLV11-KA option is installed.

Number of Data Bits – 7 or 8.

Number of Stop Bits – 1 or 2.

Parity Bit – No parity or parity; and even or odd parity.

- One channel (channel 3) can be designated the console device. In most configurations, each LSI-11 system requires one keyboard/display terminal that will function as the console device.

- All data buffers (one transmit and one receive) in each channel are double-buffered.

- Channel 3 can be configured to respond to a receive line BREAK condition by causing the processor to either halt (console emulator mode), bootstrap the system, or have no response.

- The module has on-board overload protection (fuse) for 20 mA (current loop power source to DLV11-KA option).

- The DLV11-J is completely LSI-11 bus-compatible, and will function in all present LSI-11 systems.

## **1.2 SPECIFICATIONS**

### 1.2.1 Electrical

#### M8043 Module Power Requirements

+ 5 V  $\pm$  5%, 1 A typical (1.25 A max.) + 12 V  $\pm$  3%, 0.15 A typical (0.2 A max.) Note: Add 0.225 A for each DLV11-KA option installed.

#### **Bus Loading**

ac loading = 1 unit load dc loading = 1 unit load

#### **Interface Connector Pinning**

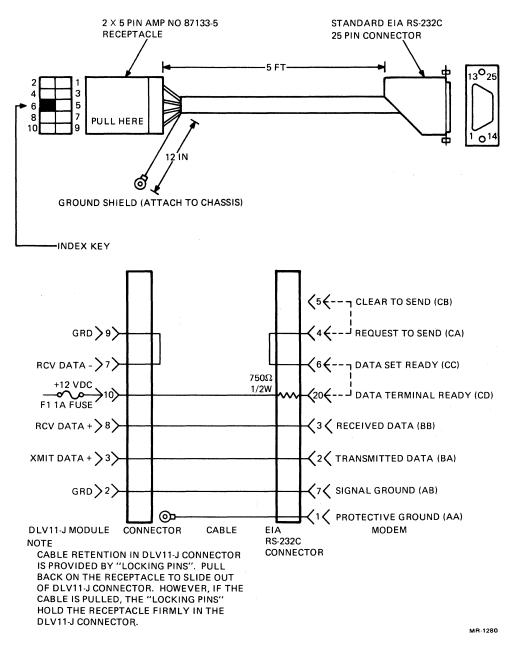

Four 10-pin connectors (one for each channel) are provided on the DLV11-J module. Connector pins and signal functions are described in Figure 1-1 and Table 1-1.

| Table 1-1 DLV11-J Connector Pinning I | Description |

|---------------------------------------|-------------|

|---------------------------------------|-------------|

| Pin | Signal/Function                                                                                        |

|-----|--------------------------------------------------------------------------------------------------------|

| 1   | UART CLK (16 × baud rate, C MOS Levels)                                                                |

| 2   | Signal Ground                                                                                          |

| 3   | Transmitted Data (EIA RS-232C, RS-423 and 20 mA);<br>Transmitted Data (+) (EIA RS-422)                 |

| 4   | Signal Ground (EIA RS-232C and RS-423);<br>Transmitted Data (-) (EIA RS-422),<br>RDR Run Pulse (20 mA) |

| 5   | Signal Ground                                                                                          |

| 6   | Indexing Key (no pin)                                                                                  |

| 7   | Received Data (-)                                                                                      |

| 8   | Received Data (+)                                                                                      |

| 9   | Signal Ground                                                                                          |

| 10  | Fused + 12 V                                                                                           |

#### Interface Signal Level

Factory Configuration: All channels are configured to meet both EIA RS-423 and RS-232C signal compatibility simultaneously.

Optional Configurations: Channels can be user-configured for EIA RS-422 or 20 mA current loop (20 mA current loop operation requires the use of the DLV11-KA 20 mA current loop option).

#### **1.2.2** Environmental

**Operating:**  $5^{\circ}$  to  $60^{\circ}$  C ( $41^{\circ}$  to  $140^{\circ}$  F) with a relative humidity of 5% to 95% (noncondensing), with adequate airflow across the module. When operating at the maximum temperature ( $60^{\circ}$  C or  $140^{\circ}$  F), air flow must maintain the inlet-to-outlet air temperature rise across the module at not more than  $5^{\circ}$  C ( $9^{\circ}$  F).

Storage: -40° to 80° C (-40° to 176° F) with a relative humidity of 5% to 95% (noncondensing).

#### NOTE

Before operating a module that has been stored in an environment outside the specified operating environment, the module must be allowed to stabilize at the operating temperature for 5 minutes (minimum).

#### 1.2.3 Physical

| Height | 13.2 cm (5.2 in) typical |

|--------|--------------------------|

| Width  | 1.27 cm (0.5 in) typical |

| Length | 22.8 cm (8.9 in) typical |

#### NOTE

Length as stated is approximate and includes plastic handles. Actual module length is 21.6 cm (8.5 in).

Weight 0.23 kg (8 oz) typical

#### **1.2.4 Module Contact Finger Identification**

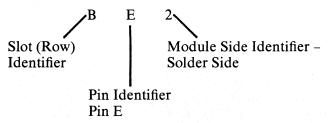

The DIGITAL finger (pin) identification for dual-height boards is shown in Figure 1-2.

#### **1.2.5 Backplane Pinning Utilization**

DLV11-J backplane pin utilization is shown in Table 1-2. Blank spaces indicate pins not used.

#### **1.3 OPTIONS**

#### 1.3.1 Cables

The DLV11-J may work in conjunction with several peripheral device cables and options, thus providing great flexibility when configuring systems. Figure 1-3 shows the possible cables and options used with the DLV11-J as well as the primary application of each.

Figure 1-2 Module Contact Finger Identification

| A Connector                               |     | B Connector |         |                           |          |

|-------------------------------------------|-----|-------------|---------|---------------------------|----------|

| Side 1                                    | Pin | Side 2      | Side 1  | Pin                       | Side 2   |

|                                           | А   | + 5 V       | BDCOK H | Α                         | +5 V     |

|                                           | В   |             |         | В                         |          |

|                                           | С   | GND         |         | C                         | GND      |

|                                           | D   | + 12 V      |         | D                         |          |

|                                           | E   | BDOUT L     |         | E .                       | BDAL2 L  |

|                                           | F   | BRPLY L     |         | F                         | BDAL3 L  |

|                                           | Н   | BDIN L      |         | H                         | BDAL4 L  |

| GND                                       | J   | BSYNC L     | GND     | J                         | BDAL5 L  |

|                                           | K   |             |         | K                         | BDAL6 L  |

|                                           | L   | BIRQ L      |         | L                         | BDAL7 L  |

| GND                                       | Μ   | BIAKI L     | GND     | М                         | BDAL8 L  |

|                                           | Ν   | BIAKO L     |         | Ν                         | BDAL9 L  |

| BHALT L                                   | Р   | BBS7 L      |         | Р                         | BDAL10 L |

|                                           | R   | BDMGI L     |         | R                         | BDAL11 L |

|                                           | S   | BDMGO L     |         | S                         | BDAL12 L |

| GND                                       | Т   | BINIT L     | GND     | Т                         | BDAL13 L |

|                                           | U   | BDAL0 L     |         | U                         | BDAL14 L |

| an an Arrian                              | V   | BDAL1 L     | + 5 V   | $\mathbf{V} = \mathbf{V}$ | BDAL15 L |

| en an |     |             |         |                           |          |

Table 1-2

Backplane Pin Utilization

Figure 1-3 DLV11-J Cabling Summary

#### 1.3.2 DLV11-KA 20 mA Current Loop Option

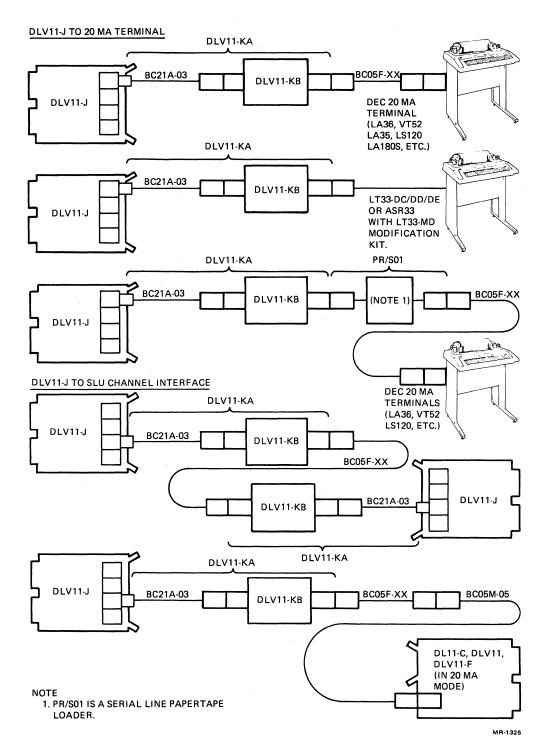

The DLV11-J module has the ability to interface with 20 mA current loop devices including those with "reader-run" capabilities. This is accomplished with the use of the DLV11-KA option. The option consists of a DLV11-KB (EIA to 20 mA current loop converter) and a BC21A-03 interface cable. The DLV11-KA is placed between the DLV11-J module output and the 20 mA current loop peripheral device. Figure 1-4 illustrates the cables and devices which may be used with the DLV11-KA option. For detailed information on the DLV11-KA option see Appendix A.

Figure 1-4 DLV11-J 20 mA Cabling Summary

# CHAPTER 2 INSTALLATION

#### 2.1 INTRODUCTION

The DLV11-J can be installed in any system that uses an LSI-11 bus structure. This includes LSI-11 and LSI-11/2 component systems, PDP-11/03, PDP-11V03, and PDP-11T03 systems.

Installation involves the following steps.

- 1. Jumpers on the DLV11-J module are configured for the specific mode of operation required by the user.

- 2. The module is installed in the LSI-11 system backplane.

- 3. Up to four peripherals (terminals, printers, etc.) can be connected to the DLV11-J module.

The DLV11-J is factory-configured for the following operation.

- Base Device Register Address = 176500

- Base Vector = 300

- Channel 3 enabled as the console device (device register addresses 177560-177566 and vectors = 60 and 64)

- Channel 3 Halt on BREAK enabled

- Baud rates (transmit and receive are identical):

Channels 0, 1 and 2 = 9.6K bits/s

- Channel 3 = 300 bits/s

- Data/parity/stop bit format (all channels):

Number of data bits = 8

Number of stop bits = 1

Parity = parity disabled

• Serial line signal interface levels (all channels) meet both Electronics Industry Association (EIA) RS-232C and RS-423 signal levels, simultaneously (slew rate =  $2 \mu s$ )

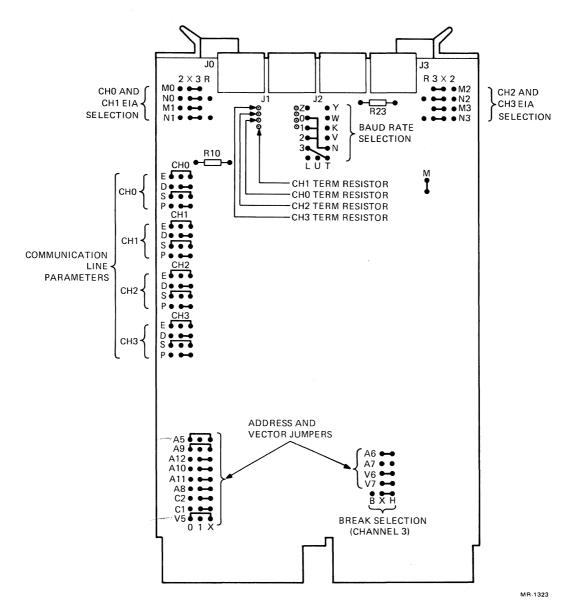

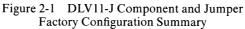

Figure 2-1 gives the location of components and jumpers used to configure the DLV11-J module to meet user requirements. Table 2-1 gives a summary of the factory configuration of these components and jumpers with a brief explanation of their purpose.

The remainder of this chapter contains specific instructions for configuring and installing the DLV11-J.

| Label                                           | Configuration                                                        | Function Implemented                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5 | X to 1<br>X to 1<br>X to 1<br>X to 0<br>X to 1<br>R*<br>I*<br>X to 0 | This arrangement of jumpers A5-A12 implements the octal base device address 1765XX, which is the assigned address for channel 0 RCSR. The least significant digit is decoded on the module during operation to address one of four SLU device registers as follows.<br>LSD = $0 = RCSR$<br>LSD = $2 = RBUF$<br>LSD = $4 = XCSR$<br>LSD = $6 = XBUF$ |

| C1<br>C2                                        | X to 1<br>X to 1                                                     | These jumpers are used to enable channel 3 for console operation. Base address must be 176500 (factory-configured), 176540 or 177500.                                                                                                                                                                                                               |

| BREAK<br>Response                               | X to H                                                               | This jumper determines channel 3 BREAK response. The board is configured for halt (con-<br>sole emulator mode) upon receiving a BREAK condition).                                                                                                                                                                                                   |

| V7<br>V6<br>V5                                  | I*<br>I*<br>X to 0                                                   | This arrangement of jumpers V5–V7 implements the octal base vector of 300 with channel 3 at 60 and 64.                                                                                                                                                                                                                                              |

| E<br>D<br>S<br>P                                | X to 0<br>X to 1<br>X to 0<br>X to 1                                 | Odd parity enabled<br>8 data bits<br>1 stop bit<br>No parity                                                                                                                                                                                                                                                                                        |

|                                                 |                                                                      | These jumpers determine the word format used by the channel. All channels are configured the same at the factory.                                                                                                                                                                                                                                   |

| 0<br>1<br>2<br>3                                | 0 to N<br>1 to N<br>2 to N<br>3 to T                                 | 9.6K baud<br>9.6K baud<br>9.6K baud<br>300 baud                                                                                                                                                                                                                                                                                                     |

|                                                 |                                                                      | These jumpers determine the baud rate (bits/s) of the serial line channel. If more than one channel requires the same baud rate, daisy-chain the wirewrap pins.                                                                                                                                                                                     |

| М                                               | I*                                                                   | Always installed, removed only during production test.                                                                                                                                                                                                                                                                                              |

| N0-N3<br>M0-M3                                  | X to 3<br>X to 3                                                     | These jumpers determine the EIA standard compatibility of the channels. All channels are set at the factory to be compatible to both EIA RS-423 and RS-232C simultaneously.                                                                                                                                                                         |

| R10                                             | 22K ohms                                                             | Channels 0 and 1 slew rate of 2 $\mu$ s (used when configured for EIA RS-423/RS-232C)                                                                                                                                                                                                                                                               |

| R23                                             | 22K ohms                                                             | Channels 2 and 3, slew rate of 2 $\mu$ s (used when configured for EIA RS-423/RS-232C)                                                                                                                                                                                                                                                              |

Table 2-1

DLV11-J Component and Jumper Factory Configuration Summary

\*R = jumper removed; I = jumper installed

•

#### **2.2 CONFIGURING MODULE JUMPERS**

#### 2.2.1 General

The DLV11-J device register addresses, interrupt vectors, serial word formats, baud rates, etc., are selected by installing and/or removing jumpers. Wirewrap posts are provided on the module for this purpose. The module is factory-configured and ready for use in many user applications. However, as your system applications require different DLV11-J device register addresses and interrupt vectors and/or operations, refer to appropriate paragraphs for configuration instructions.

#### 2.2.2 Addressing